## **Copyright Notice**

All Sample Papers and Past Papers are copyright of the British Computer Society.

All rights reserved. No part of these papers may be reproduced in any form except as permitted by the Copyright Designs and Patents Act 1988. Enquiries for permission to reproduce any or parts of this material should be directed to the British Computer Society.

The British Computer Society

1 Sanford Street Swindon, Wiltshire United Kingdom SN1 1HJ

Tel: +44 (0)1793 417424 Fax: +44 (0)1793 480270 E-mail: bcshq@hq.bcs.org.uk

## THE BRITISH COMPUTER SOCIETY

## THE BCS PROFESSIONAL EXAMINATION Diploma

## **ARCHITECTURE**

27<sup>th</sup> April 2000 - 10:00a.m. - 12:00p.m. Answer FOUR questions out of SIX. All questions carry equal marks. Time: TWO hours

The marks given in brackets are indicative of the weight given to each part of the question.

- 1. A burglar alarm control system has four inputs. Three inputs are derived from sensors which output logic true signals if an intruder is detected in their respective zones. The fourth input indicates the presence of an error condition if it goes true. The alarm will only be sounded if at least two sensors detect an intruder and an error condition is not indicated.

- a) Produce a truth table for the state of the alarm.

(3 marks)

- b) Use a Karnaugh map to find a minimised sum of products expression for the state of the alarm. (3 marks)

- c) Draw a logic circuit for the minimised form of the alarm expression using only NOT, AND and OR gates. (5 marks)

- d) Manipulate the minimised sum of products expression into a suitable form and hence draw a logic circuit for the alarm using only NAND gates. (5 marks)

- e) Manipulate the minimised sum of products expression into a suitable form and hence draw a logic circuit for the alarm using only NOR gates. (5 marks)

- f) Compare the relative merits of the NOT, AND and OR, NOR and NAND implementations for the logic circuit of the alarm. (4 marks)

- 2. a) What is the OSI 7-layer model? Your answer should include the following:

- i) a description of the model together with a diagram;

- ii) a short description of the services supplied by each layer.

(N.B. It is not sufficient merely to list the names of each layer.)

(12 marks)

b) List the essential components of a data link layer data frame.

(6 marks)

What is meant by the term flow control? Explain how this concept might be implemented using the HDLC protocol.

(7 marks)

- 3. a) Each peripheral device installed in a computer system requires an interface. Discuss the roles that such an interface is required to perform. (7 marks)

- b) Explain the principles of the *software poll* and *interrupt request* strategies for input/output control and discuss their relative merits. (12 marks)

- c) List the factors which determine the interrupt response time of an interface used in a computer system (i.e. the delay time between the interrupt request being asserted and the first instruction of the interrupt service routine being executed). (6 marks)

- 4. a) Discuss the precautions you would take in the design of synchronous counters to ensure correct operation immediately after power is applied to the circuit. (5 marks)

- b) The count sequence for a 2\*421 counter is shown in the table below:

| D | С | В | Α |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 0 | 1 |

| 1 | 1 | 1 | 0 |

| 1 | 1 | 1 | 1 |

| 0 | 0 | 0 | 0 |

- i) Draw a state diagram for the 2\*421 counter.

- ii) Give the excitation tables for a synchronous 2\*421 counter based on JK flip-flops.

- iii) Give the minimised sum of products expression for each excitation signal.

- iv) Draw the logic circuit for a synchronous 2\*421 counter.

(20 marks)

- 5. a) Describe the terms:

- i) Sector;

- ii) Track;

- iii) Cylinder;

- iv) Partition;

as applied to a hard disk.

(6 marks)

b) What is meant by the term File Allocation Table (FAT)?

(7 marks)

c) Explain how a 4500 byte file called **README.DAT** would be held in a properly configured 60 Mbyte DOS (FAT16) partition. (12 marks)

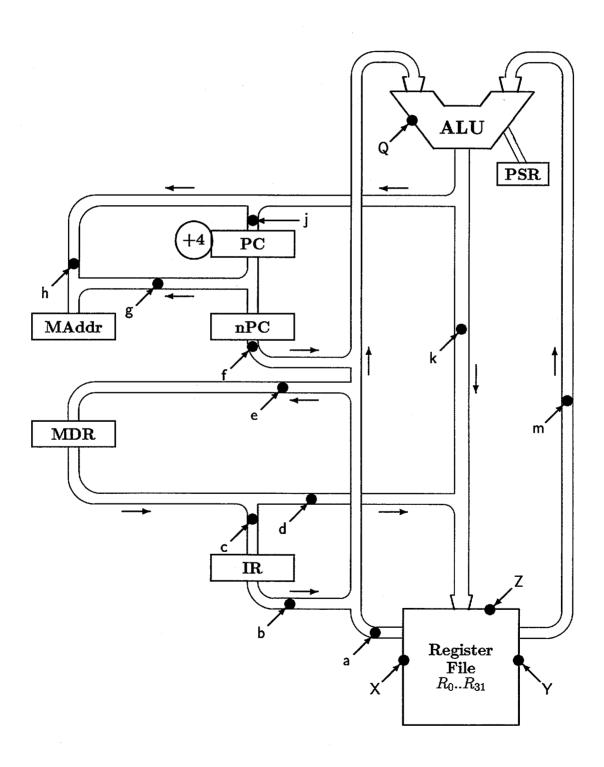

- 6. a) Study the outline diagram of a CPU below and describe the steps and data flows in the execution of an add store to register instruction. (9 marks)

- b) Using your description above, estimate the time required to execute the add instruction if the store access time is 15nS and the CPU clock frequency is 200MHz. (8 marks)

- c) Describe **TWO** mechanisms used by the designers of such a CPU to improve its performance. Estimate the performance improvement resulting from the use of each mechanism. (8 marks)