# **2011 Electronic and Electrical Fundamentals**

## **Intermediate 2**

# **Finalised Marking Instructions**

© Scottish Qualifications Authority 2011

The information in this publication may be reproduced to support SQA qualifications only on a non-commercial basis. If it is to be used for any other purposes written permission must be obtained from SQA's NQ Delivery: Exam Operations Team.

Where the publication includes materials from sources other than SQA (secondary copyright), this material should only be reproduced for the purposes of examination or assessment. If it needs to be reproduced for any other purpose it is the centre's responsibility to obtain the necessary copyright clearance. SQA's NQ Delivery: Exam Operations Team may be able to direct you to the secondary sources.

These Marking Instructions have been prepared by Examination Teams for use by SQA Appointed Markers when marking External Course Assessments. This publication must not be reproduced for commercial or trade purposes.

### Section A

### Attempt all the questions in this section (50 marks)

**1.** Convert the following numbers.

| (a)     | Binary to dec          | imal    |                  | 10101111 <sub>2</sub> |

|---------|------------------------|---------|------------------|-----------------------|

| (b)     | Decimal to Hexadecimal |         |                  | 123 <sub>10</sub>     |

| (c)     | Hexadecimal            | to Bina | ary              | CD <sub>16</sub>      |

| Answers |                        |         |                  |                       |

| (a)     | 10101111 <sub>2</sub>  | =       | <b>175</b> 10    | 2                     |

| (b)     | 123 <sub>10</sub>      | =       | 7B <sub>16</sub> | 2                     |

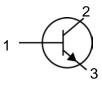

(c)  $CD_{16} = 11001101_2$  2 (6) 2. Identify the pin connections for the circuit symbols shown in Figure Q2(*a*) and Figure Q2(*b*).

(a)

Figure Q2(b)

| (a) | 1 = base, 2 = collector, 3 = emitter | 3        |

|-----|--------------------------------------|----------|

| (b) | 1 = gate, 2 = drain, 3 = source      | 3<br>(6) |

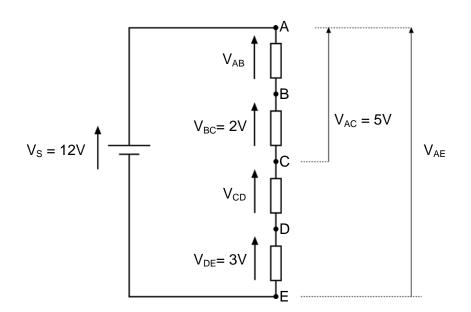

- **3.** (a) For the circuit shown in Figure Q3(a) below, determine:

- (i) the voltage  $V_{AE}$ ;

- (ii) the voltage  $V_{AB}$ ;

- (iii) the voltage  $V_{CD}$ ;

Figure Q3*(a)*

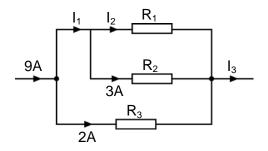

- (b) For the circuit shown in Figure Q3(b) below, determine:

- (i) I<sub>1</sub>;

- (ii)  $I_2$ ;

- (iii) I<sub>3</sub>;

Figure Q3(b)

| (a) | (i)   | $V_{AE} = 12V$      | 1        |

|-----|-------|---------------------|----------|

|     | (ii)  | $V_{AB} = 3V$       | 1        |

|     | (iii) | $V_{CD} = 4V$       | 1        |

| (b) | (i)   | I <sub>1</sub> = 7A | 1        |

|     | (ii)  | $I_2 = 4A$          | 1        |

|     | (iii) | $I_3 = 9A$          | 1<br>(6) |

Marks

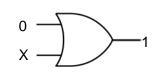

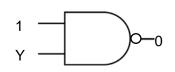

- **4.** Determine the logic input X, Y and Z for each of the guests in Figure Q4(*a*), Figure Q4(*b*) and Figure Q4(*c*).

- (a)

Figure Q4*(a)*.

(b)

Figure Q4(b).

(C)

Figure Q4(c).

#### Answers

(a) X = 1 1

(c)

$$Z = 0$$

(3)

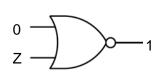

- **5.** For the circuit shown in Figure Q5:

- (a) name the circuit configuration;

- (b) determine the circuit gain.

Figure Q5

| (a) | Common Source Amplifier or FET Amplifier.  | 1        |

|-----|--------------------------------------------|----------|

| (b) | Gain = $V_{out}/Vin = 10/0.25 = 40$ or -40 | 2<br>(3) |

6. Figure Q6 shows a current carrying conductor placed between the poles of a magnet.

State the effect on the force acting upon the conductor when:

- (a) the current is doubled;

- (b) the current direction is reversed;

- (c) the poles are reversed;

- (d) a stronger magnet is used.

| (a) | Force doubles or increases          | 1        |

|-----|-------------------------------------|----------|

| (b) | Force changes direction or reversed | 1        |

| (c) | Force changes direction or reversed | 1        |

| (d) | Force is stronger                   | 1<br>(4) |

- 7. The diagram in Figure Q7 includes a variable resistor ( $R_v$ ) that can be varied between 1 k $\Omega$  and 10 k $\Omega$ .

- (a) Determine the output voltage (pk-pk) when  $R_V$  is 8 k $\Omega$ .

- (b) Determine the minimum value of output voltage (pk-pk).

- (c) Explain why an output voltage of 500 mV (pk-pk) is not achievable with the 50 mV (pk-pk) input voltage.

- (d) Determine the new value of input voltage that would enable an output voltage of 500 mV (pk-pk) to be achieved when  $R_V$  is set for maximum gain.

Figure Q7

| (a) | $V_{out} = 4 \times 50m = 200m V pk-pk$                                               | 2        |

|-----|---------------------------------------------------------------------------------------|----------|

| (b) | $V_{out min} = \frac{1}{2} \times 50 \text{m V} = 25 \text{m V pk-pk}$                | 2        |

| (c) | A $V_{\text{out}}$ OF 500M v requires a gain of 10 but the maximum possible is only 5 | 2        |

| (d) | $V_{IN} = V_{OUT}/Gain = 500m V/5 = 100m V pk-pk$                                     | 2<br>(8) |

**8.** For the circuit shown in figure Q8.

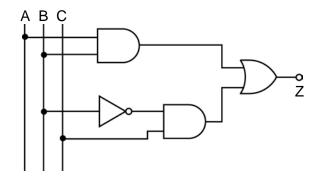

Figure Q8

- (a) determine the Boolean expression for output Z;

- (b) draw the truth table for the circuit.

- (c) A fault condition causes the invertor output to be permanently High. Complete the truth table for this condition.

#### Answers

(a)

$$Z = A.B + \overline{B}.C$$

(b)&(c)

|   |   |   | 1   | 2   | 1 + 2 | Fault |

|---|---|---|-----|-----|-------|-------|

| А | В | С | A.B | B.C | Z     | Z     |

| 0 | 0 | 0 | 0   | 1   | 0     | 0     |

| 0 | 0 | 1 | 0   | 0   | 1     | 1     |

| 0 | 1 | 0 | 0   | 1   | 0     | 0     |

| 0 | 1 | 1 | 0   | 1   | 0     | 1     |

| 1 | 0 | 0 | 0   | 1   | 0     | 0     |

| 1 | 0 | 1 | 0   | 0   | 1     | 1     |

| 1 | 1 | 0 | 1   | 1   | 1     | 1     |

| 1 | 1 | 1 | 1   | 1   | 1     | 1     |

(8)

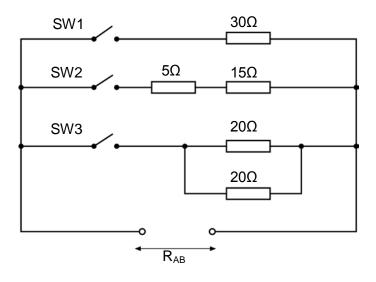

**9.** For the circuit shown in Figure Q9, state:

Figure Q9

- (a) which switch(es) should be closed to give minimum R<sub>AB</sub>;

- (b) which switch(es) should be closed to give maximum R<sub>AB</sub>;

- (c) which switch(es) should be closed to make  $R_{AB}$  12 $\Omega$ .

| (C) | SW1 & SW2                 | 2<br>(6) |

|-----|---------------------------|----------|

|     | SW1                       | 2        |

| (a) | All SW's should be closed | 2        |

#### Section B

#### Attempt any TWO questions in this section (50 marks) Each question is worth 25 marks

- **10.** Add the following binary numbers.

- (a) (i)  $0011_2 + 0111_2$

- (ii)  $0100_2 + 0111_2$

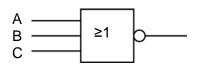

- (b) State the Boolean expression and construct the truth table for the following logic gate.

(c) Using the datasheet provided, select the required logic chip and mark the logic chip number and pin numbers on the logic diagram on Worksheet Q10(c).

Note: You may use any of the 6 logic chips and each logic chip may only be used once.

(d) Draw, using BS symbols, the logic diagram for the following Boolean expression and determine the truth table.

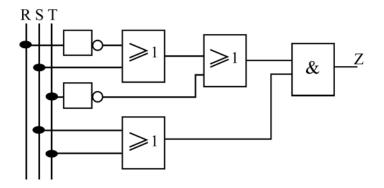

$Z = (\overline{R} + S + \overline{T}).(S + T)$

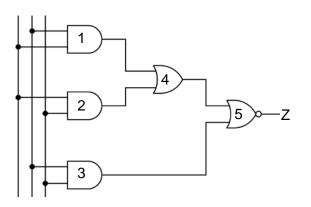

(e) The circuit shown below Figure 10(e)(i) has developed a fault and upon testing the outputs shown in the truth table Figure 10(e)(i) were obtained. Determine which gate (input or output) is at fault and state the nature of the fault.

Figure 10(e)(i)

| Δ | Р | <u> </u> | 7 |

|---|---|----------|---|

| A | В | С        | Z |

| 0 | 0 | 0        | 1 |

| 0 | 0 | 1        | 1 |

| 0 | 1 | 0        | 1 |

| 0 | 1 | 1        | 1 |

| 1 | 0 | 0        | 1 |

| 1 | 0 | 1        | 0 |

| 1 | 1 | 0        | 0 |

| 1 | 1 | 1        | 0 |

Figure 10*(e)*(ii)

#### Answers

(a) (i)

$$0011_2 + 0111_2 = 1010_2$$

2

(ii)

$$0100_2 + 0111_2 = 1011_2$$

**2**

$$(b) Z = \overline{A + B + C} 1$$

| А | В | С | Z |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 0 |

### (c) See Worksheet

(d)

$$Z = (\overline{R} + S + \overline{T}).(S + T)$$

6

2

2

| R | S | Т | R+S+T | S + T | Z |

|---|---|---|-------|-------|---|

| 0 | 0 | 0 | 1     | 0     | 0 |

| 0 | 0 | 1 | 1     | 1     | 1 |

| 0 | 1 | 0 | 1     | 1     | 1 |

| 0 | 1 | 1 | 1     | 1     | 1 |

| 1 | 0 | 0 | 1     | 0     | 0 |

| 1 | 0 | 1 | 0     | 1     | 0 |

| 1 | 1 | 0 | 1     | 1     | 1 |

| 1 | 1 | 1 | 1     | 1     | 1 |

(e)

4

|   |   |   | 1         | 2   | 1+2 | INV |       |

|---|---|---|-----------|-----|-----|-----|-------|

| Α | В | С | (A,B)+A.C | B.C |     | Z   | FAULT |

| 0 | 0 | 0 | 0         | 0   | 0   | 1   | 1     |

| 0 | 0 | 1 | 0         | 0   | 0   | 1   | 1     |

| 0 | 1 | 0 | 0         | 0   | 0   | 1   | Į     |

| 0 | 1 | 1 | 0         | 1   | 1   | (0  | 1)    |

| 1 | 0 | 0 | 0         | 0   | 0   | ł   |       |

| 1 | 0 | 1 | 1         | 0   | 1   | 0   | 0     |

| 1 | 1 | 0 | 1         | 0   | 1   | 0   | 0     |

| 1 | 1 | 1 | 1         | 1   | 1   | 0   | 0     |

Marks awarded for construction/derivation of truth table and identifying the location of the faulty output.

Fault occurs when input B and C are on and the output of gate 3 and/or the input of gate 5 is held low.

2

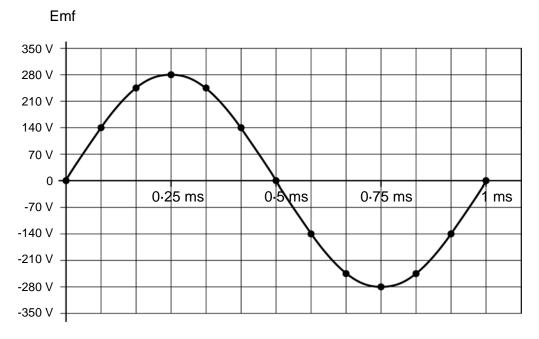

**11.** (a) For the wave form to be shown in Figure Q11(a) determine:

- (i) the peak value of the voltage;

- (ii) the rms value;

- (iii) the period of the waveform.

- (b) (i) A coil of length 0.5m is moved through a magnet field of 0.25 T at a speed of  $10 \text{ ms}^{-1}$ . Calculate the induced voltage.

- (ii) The same coil is now inserted in a management field of 1.2 T and is connected to a supply. Determine the current flowing in the conductor if the force on the conductor is measured at 2.4 N.

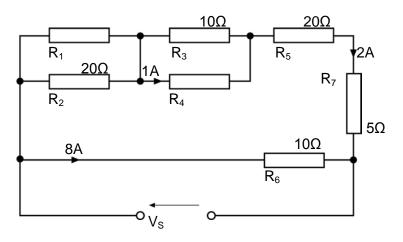

- (c) For the circuit shown in Figure Q11(c) determine:

Figure Q11(c)

(i) the supply voltage  $V_s$ ;

- (ii) the total circuit resistance;

- (iii) the current through resistor R<sub>3</sub>;

- (iv) the voltage across resistor R<sub>3</sub>;

- (v) the value of resistor  $R_4$ ;

- (vi) the voltage across resistor  $R_1$ ;

- (vii) The value of resistor  $R_1$ .

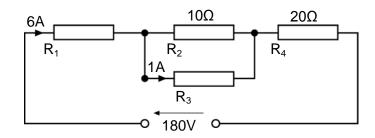

- (*d*) For the circuit shown in Figure Q11(*d*) determine:

Figure Q11(d)

- (i) the power dissipated in the  $10\Omega$  resistor R<sub>2</sub>;

- (ii) the total power dissipated in the circuit;

- (iii) the energy consumed, in Joules, if the circuit is operated for 2 hours.

| (a) | (i)   | The peak value is <b>280V</b>                                                        | 1 |

|-----|-------|--------------------------------------------------------------------------------------|---|

|     | (ii)  | The rms = 280 x 0.707 = <b>197-96V</b>                                               | 2 |

|     | (iii) | Period = <b>1ms</b>                                                                  | 1 |

| (b) | (i)   | E = B x I x v = 0.25 x 0.5 x 10 = <b>1.25V</b>                                       | 2 |

|     | (ii)  | F = B x   x   hence $I = F/(B x 1)$                                                  | 3 |

|     |       | I = 2.4/(1.2 x .5) = <b>4A</b>                                                       |   |

| (c) | (i)   | $V_{\rm S} = I_{\rm R6} \ x \ R_6 = 8 \ x \ 10 = 80V$                                | 2 |

|     | (ii)  | $I_T = I_{R6} + I_{R5} = 8 + 2 = 10A$                                                | 2 |

|     |       | $R_{T} = V_{S}/I_{T} = 80/10 = 8\Omega$                                              |   |

|     | (iii) | Current in $R_3$ (by Kirchhoff's) = 2 - 1 = <b>1A</b>                                | 1 |

|     | (iv)  | $V_{R3} = I_{R3} \times R_3 = 1 \times 10 = 10V$                                     | 1 |

|     | (v)   | $R4 = V_{R3}/I_{R4} = 10/1 = 10\Omega$ or                                            | 1 |

|     |       | As $I_{R3} = I_{R4}$ and $V_{R3} = V_{R4}$ then $R_3 = R_4$                          |   |

|     | (vi)  | $V_{R3} = 10V; V_{R5} = 2 \times 20 = 40V; V_{R7} = 2 \times 5 = 10V;$               | 2 |

|     |       | Therefore by Kirchhoff's                                                             |   |

|     |       | $V_{R1} = V_s - V_{R3} - V_{R5} - V_{R7} = 80 - 1 - 40 - 10 = 20V$                   |   |

|     | (vii) | $R_1$ , $R_2$ combination = $V_{R1}/I_{R1}$ + $I_{R2}$ = 20/2 = 10 $\Omega$          | 2 |

|     |       | Therefore as $R_2 = 20\Omega$ then $R_1$ must = <b>20</b> $\Omega$                   |   |

|     |       | Or                                                                                   |   |

|     |       | $I_{R2} = V_{R1}/R_2 = 20/20 = 1A$ therefore by Kirchhoff's                          |   |

|     |       | $I_{R1} = I_{R7} - I_{R2} = 2 - 1 = 1A$ hence $R1 = V_{R1}/I_{R1} = 20/1 = 20\Omega$ |   |

| (d) | (i)   | $I_{R2} = 6 - 1 = 5A$                                                                | 2 |

|     |       | $P = I^2 x R = 5 x 5 x 10 = 250W$                                                    |   |

|     | (ii)  | PT = V <sub>S</sub> x I <sub>S</sub> = 180 x 6 = <b>1080W</b>                        | 1 |

|     | (iii) | E = P x t = 1080 x 2 x 60 x 60 = <b>7776000J = 7.776MJ</b>                           | 2 |

|     |       |                                                                                      |   |

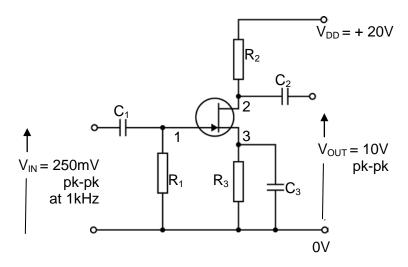

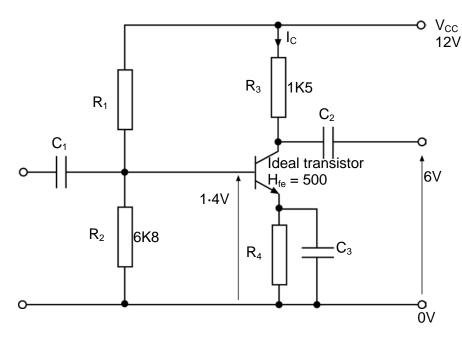

**12.** (a) Identify the circuit shown in Figure Q12(a) and identify the purpose of each of the capacitators  $C_1$ ,  $C_2$ , and  $C_3$ .

- (b) For the circuit shown in Figure Q12(a) calculate:

- (i) the collector current  $I_C$ ;

- (ii) the base current I<sub>b</sub>;

- (iii) the current through the resistor R<sub>2</sub>;

- (iv) the value of the resistor  $R_1$ .

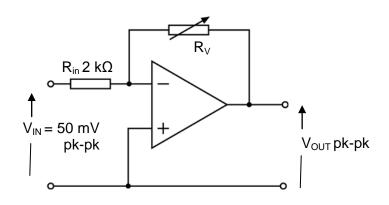

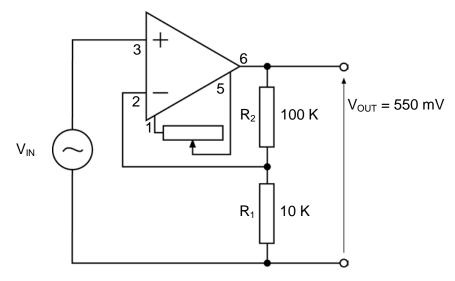

- (c) For the circuit shown in Figure Q12(c).

Figure Q12(c)

- (i) Identify the circuit configuration shown in Figure Q12(c).

- (ii) Determine the gain of the circuit and the input voltage.

- (iii) When setting up the circuit it is found that for an input of 0 V the output is not zero. What component in Figure Q12(c) will allow the output to be adjusted to zero? What is this process called?

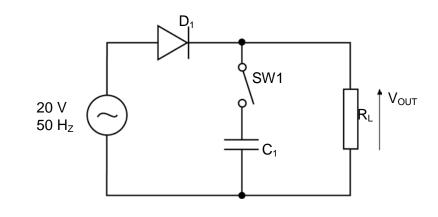

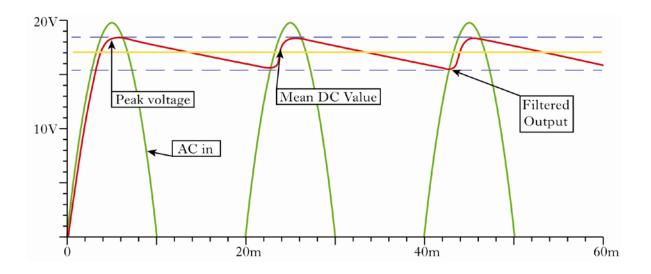

Figure Q12(d)

Sketch the output waveform for the circuit in Figure Q12(d) with

(A) SW1 open, and

(d)

(B) SW1 closed.

| 12. | (a) | Common Emitter Amplifier<br>C1: - Coupling Capacitor<br>C2: - Coupling Capacitor<br>C3: - Decoupling Capacitor or Bypass Capacitor | 1<br>1<br>1 |

|-----|-----|------------------------------------------------------------------------------------------------------------------------------------|-------------|

|     | (b) | (i) By Kirchhoff's $V_{R3} = V_S - V_{OUT} = 12 - 6 = 6V$                                                                          | 2           |

|     |     | $I_{R3} = V_{R3}/R_3 = 6/1500 = 4mA$                                                                                               |             |

|     |     | (ii) Gain = 500 = Ic/Ib hence Ib = I c/Gain = 4mA/500 = <b>8µA</b>                                                                 | 2           |

|     |     | (iii) $I_{R2} = V_{R2}/R_2 = 1.4/6800 = 206 \mu A$                                                                                 | 2           |

|     |     | (iv) $I_{R1} = + Ib = 206 + 8 = 214 \mu A$                                                                                         | 2           |

|     |     | $I_{R1} = V_S - V_{R2} = 12 - 1.4 - 10.6V$                                                                                         |             |

|     |     | Hence R <sub>1</sub> = C/I <sub>R1</sub> = 10.6/214μA = <b>49.53kΩ</b>                                                             |             |

|     | (c) | (i) Non inverting Op Amp                                                                                                           | 1           |

|     |     | (ii) Gain = $(R_2/R_1) + 1 = (100/10) + 1 = 10 + 1 = 11$                                                                           | 2           |

|     |     | (iii) Gain = V <sub>out</sub> /Vin<br>Hence Vin = V <sub>out</sub> /gain = 550m V/11 = 50m V                                       | 2           |

|     | (d) | $V$ $F = 50H_Z$ $V_{out} = 19.3V pk$                                                                                               |             |

|     |     | (A) By adjusting the variable resistor Rv                                                                                          | 1           |

|     |     | (B) Offset Null adjustment                                                                                                         | 2           |

## [END OF MARKING INSTRUCTIONS]