ANALOG & DIGITAL ELE

# **TYPICAL QUESTIONS & ANSWERS**

#### PART – I

#### **OBJECTIVE TYPE QUESTIONS**

#### Each Question carries 2 marks.

#### Choose correct or the best alternative in the following:

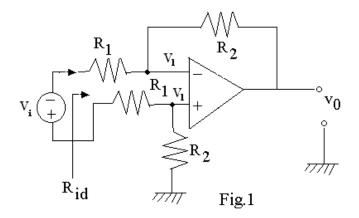

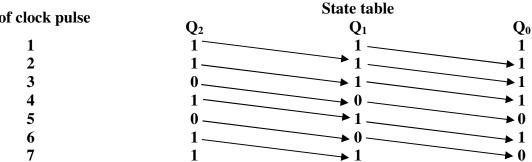

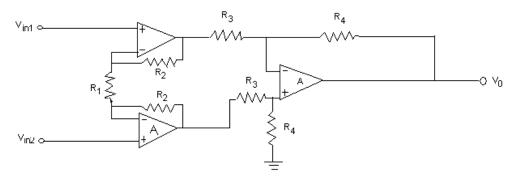

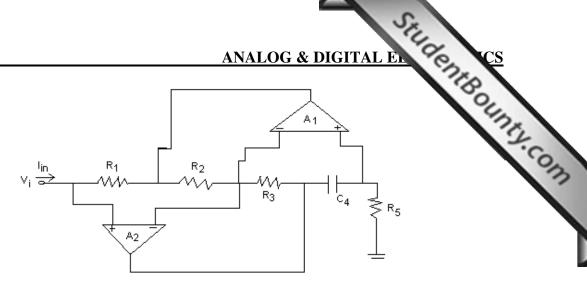

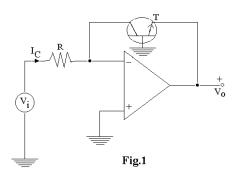

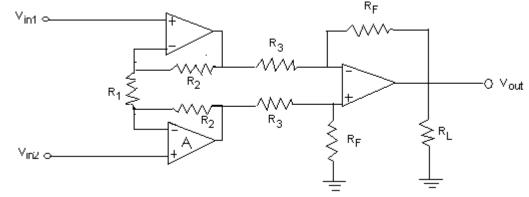

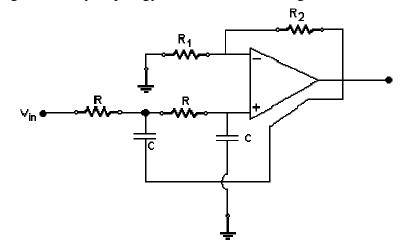

Q.1 For the circuit shown in Fig.1, the input resistance R<sub>id</sub> will be

| (A) $2R_1$ .         | <b>(B)</b> $2R_1 + R_2$ . |

|----------------------|---------------------------|

| (C) $2(R_1 + R_2)$ . | ( <b>D</b> ) Infinity     |

Ans: A

$R_{id} = \frac{v_i}{i_i}$  where  $i_i$  is the current drawn from the source. Since the two input terminals of OPAMP track each other in potential therefore writing loop equation- $v_i = R_1 i_i + 0 + R_i i_i$  thus Rid =  $R_{id} = \frac{v_i}{i_i} = 2R_1$

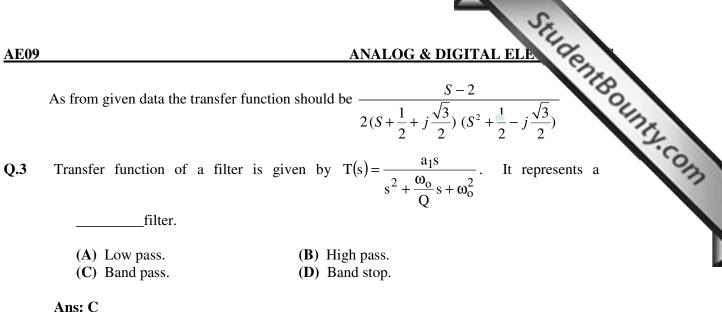

Q.2 A second order filter has its poles at  $s = -\frac{1}{2} \pm j\sqrt{3}/2$ . The transmission is zero at  $\omega = 2 \operatorname{rad}_{8}'$  and is unity at  $\omega = 0$ . The transfer function of the filter is (A)  $\frac{1}{4} \frac{\left(s^{2} + s\right)}{\left(s^{2} - s + 1\right)}$ . (B)  $\frac{1}{4} \frac{\left(s^{2} + s\right)}{\left(s^{2} + s + 1\right)}$ . (C)  $\frac{1}{4} \frac{\left(s^{2}\right)}{\left(s^{2} + s + 0.25\right)}$ . (D)  $\frac{1}{4} \frac{\left(s^{2} - s\right)}{\left(s^{2} - s - 1\right)}$ . Ans: Answer should be  $\frac{S-2}{2(S^{2} + S - \frac{1}{2})}$

#### www.StudentBounty.com Homework Help & Pastpapers

- **Q.4** In applications where measurement of a physical quantity is involved, the OPAMP circuit recommended is

- (A) Basic non-inverting amplifier. (B) A comparator.

- (C) An active filter.

- (**D**) An instrumentation amplifier.

#### Ans: D

**AE09**

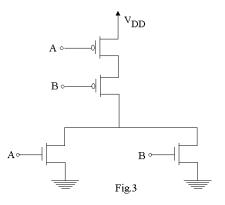

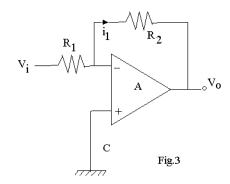

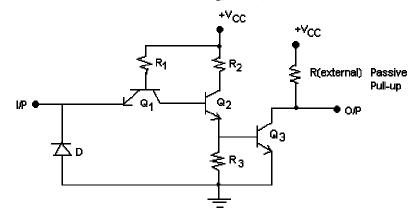

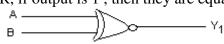

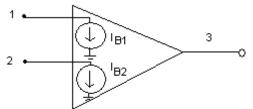

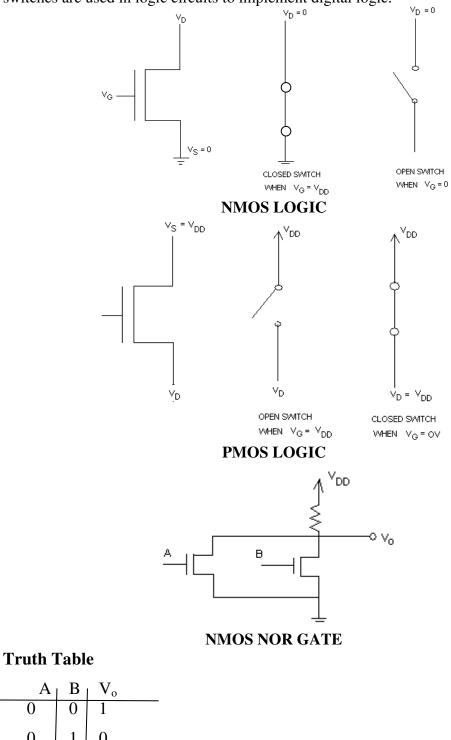

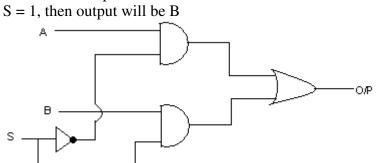

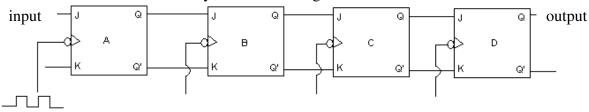

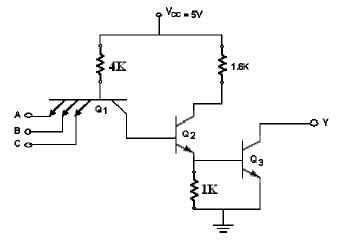

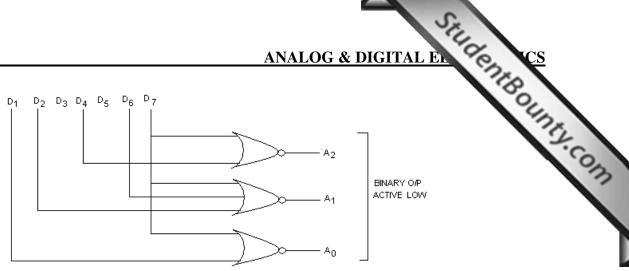

- Q.5 The circuit shown in Fig.3 represents \_\_\_\_\_ gate

- (A) AND.

- (B) NAND.

- (C) OR.

- **(D)** NOR.

#### Ans: D

- **Q.6** Active loaded MOS differential circuit has a

- (A) high CMRR. (**B**) low CMRR. (C) high delay. (**D**) high differential gain.

#### Ans: D

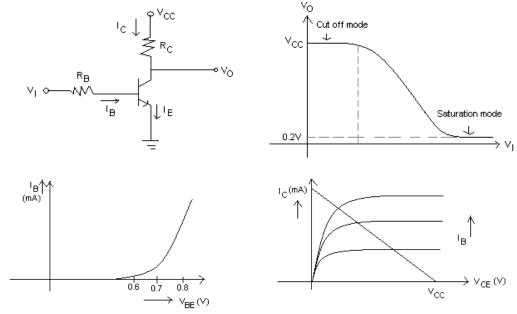

**Q.7** NPN transistor is not suitable for good analog switch because

- (A)  $I_C V_{CE}$  characteristic curve pass directly through origin.

- (B) the device has very high input impedance.

- (C) the device is asymmetrical with an offset voltage  $V_{CE}$  off.

- (**D**) it has well defined transition frequency  $f_{T}$ .

#### Ans: C

- **Q.8** CMOS logic has the property of

- (A) increased capacitance and delay.(B) decreased area.

- (C) high noise margin. (D) low static power dissipation.

| <u>AE09</u> |                                          | ANALOG & DIGITAL ELE<br>ANALOG & DIGITAL ELE<br>(B) $10^3 \Omega$ .<br>(D) $10^6 \Omega$ . |

|-------------|------------------------------------------|--------------------------------------------------------------------------------------------|

|             | Ans: D                                   | . Sta                                                                                      |

| Q.9         | The order of input resistance in 74      | 1 OPAMP is                                                                                 |

| -           | (A) 1 to $10^4 \Omega$ .                 | <b>(B)</b> $10^3 \Omega$ .                                                                 |

|             | (C) $10^5 \Omega$ .                      | ( <b>D</b> ) $10^{6}\Omega$ .                                                              |

|             | Ans: D                                   |                                                                                            |

| Q.10        | The ratio of change in input offs called | et voltage when variation in supply voltage is made is                                     |

|             | (A) PSRR.                                | ( <b>B</b> ) CMRR .                                                                        |

|             | (C) transient response.                  | (D) input offset voltage stability.                                                        |

|             | Ans: A                                   |                                                                                            |

| 0.11        | The equiripple response filter i         | s called while maximally flat time delay                                                   |

The equiripple response filter is called \_\_\_\_\_, while maximally flat time delay **V.11** response is given by \_\_\_\_\_\_ filter.

- (A) Chebyshev, Bessel.

- (C) Bessel, Chebyshev.

#### Ans: D

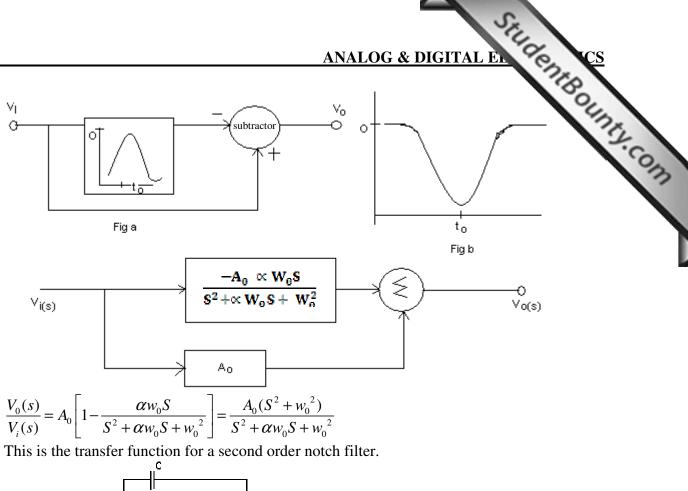

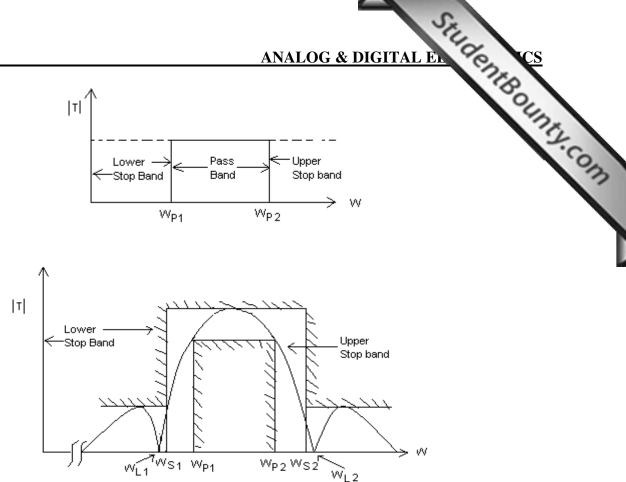

- Q.12 A notch filter is a

- (C) Wide band reject filter.

- (A) Wide band pass filter.(B) Narrow band pass filter.(C) Wide band reject filter(D) Narrow band reject filter

(**B**) Butter worth, Bessel.

(D) Chebyshev, Butter Worth.

(D) Narrow band reject filter.

#### Ans: D

Q.13 The problem faced by switched capacitor filters is

- (A) aliasing **(B)** amplitude distortion

- (C) slower roll off rate (D) longer time and phase delay

Ans: Only draw back with switched capacitor filters is that they generate more noise than active filter circuits.

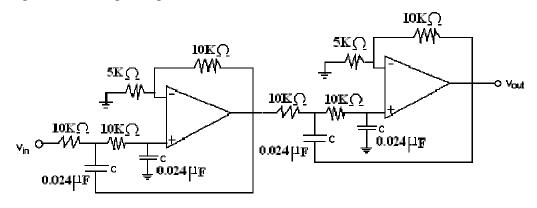

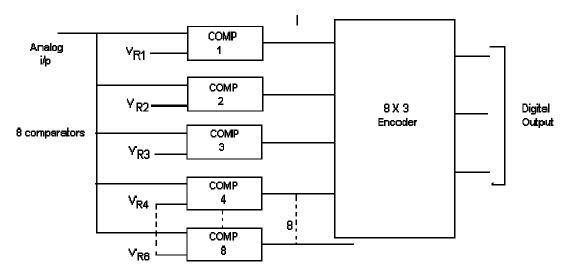

- For a 3-bit flash ADC, the number of comparators required are **Q.14**

- (A) 5 **(B)** 9 **(C)** 7 **(D)** 3

#### Ans: C

0.15 The typical quiescent power dissipation of low-power CMOS units is

| ( <b>A</b> ) 1mW. | <b>(B)</b> 0.5 mW. |

|-------------------|--------------------|

| (C) 2 nW.         | <b>(D)</b> 50 nW.  |

#### Ans: C

- Q.16 The access times of MOSRAMS is approximately

- **(B)** 80 ns. (A) 35 ns. (**C**) 400 ns. **(D)** 20 ns.

Ans: Question seems to be invalid as it is not mentioned weather static or dynamic RAM and access time varies by large magnitude from chip to chip.

#### www.StudentBounty.com nework Help & Pastpapers

- ANALOG & DIGITAL ELE Q.17 For which of the following flip-flops, the output is clearly defined for all combination two inputs.

- (A) D type flip-flop. (C) J-K flip-flop.

(B) R-S flip-flop. (D) none of these.

Ans:C

- Q.18 Active load is used in the collector of the difference amplifier of an Op-amp:

- (A) To increase the output resistance.

- (B) To increase the differential gain.

- (C) To handle large signals.

- (D) To provide symmetry.

#### Ans: B

- Q.19 A second order filter has a transfer function

- $T(S) = \frac{s^2 + 4}{s^2 + s + 1}$  the poles and zeros of this filter are at (A)  $\omega = 2, s = 0.5 \pm j\sqrt{3}/2.$  (B)  $\omega = 1, s = -1 \pm j\sqrt{3}.$ (C)  $\omega = 2, s = -1 \pm j\sqrt{3}.$  (D)  $\omega = 1, s = -0.5 \pm j\sqrt{3}/2.$

#### Ans: A

For given transfer function poles are  $0.5 \pm j \frac{\sqrt{3}}{2}$  and zeroes are  $\pm 2j$

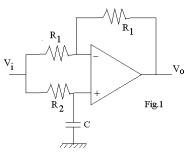

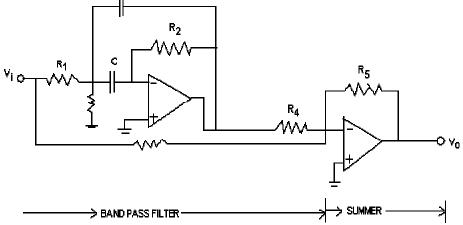

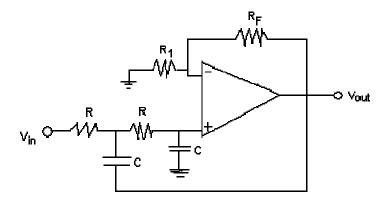

- Q.20 The circuit shown in Fig.1 represent a

- (A) Low pass filter.

- (B) High pass filter.

- (C) Band pass filter.

- (D) None of the above.

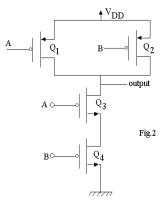

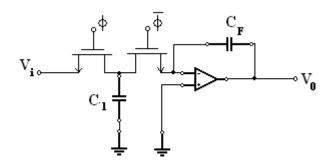

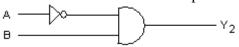

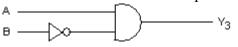

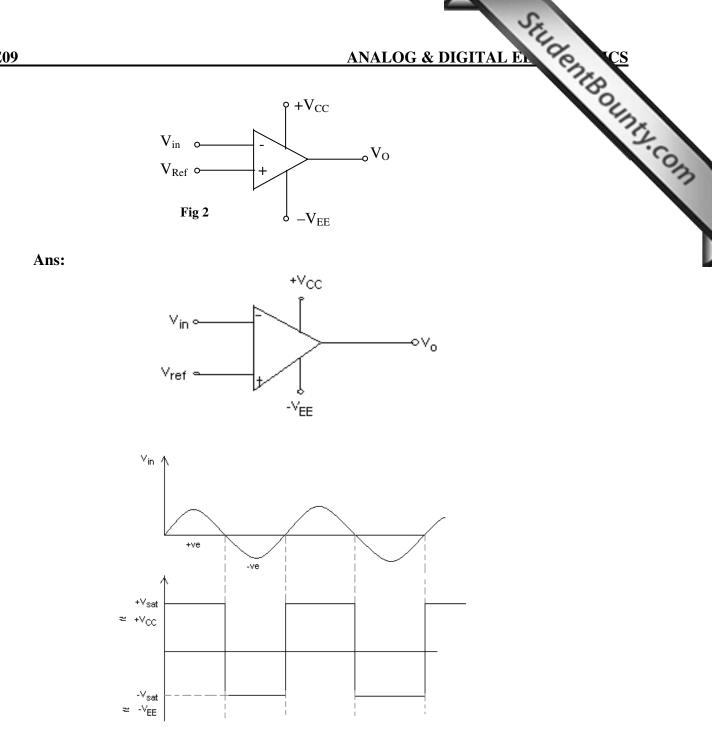

- **Q.21** The circuit in Fig.2 is used to realize the logic function of

- (A) Inverter.

- (B) NOR gate.

- (C) NAND gate.

- (D) XOR gate.

#### ANALOG & DIGITAL ELE

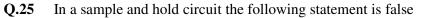

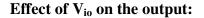

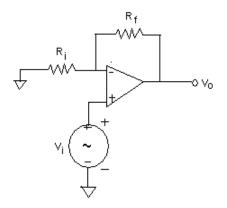

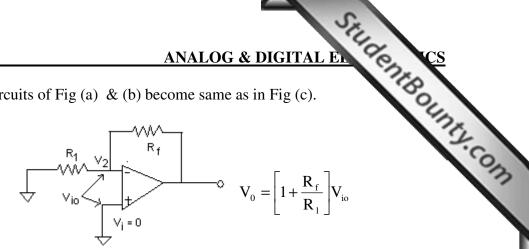

StudentBounty.com Consider an inverting op amp circuit at Fig.3 with feedback resistor equal to 100 k Q.22 the input resistor equal to 1K $\Omega$  with a gain of 100 if the op amp has infinite open loop

If the op amp has a finite open loop gain at  $10^4$ ; the gain of the op amp circuit is

(A) 100. **(B)** 101. (C) 98. (D) 99.

Ans: D

$\frac{-A_{OL} \times R_F}{R_F + R_1 (1 + A_{OL})} = 99$  Putting the values we get gain as 99 As. Gain =

Q.23 For standard TTL logic circuits, the values of V<sub>OL</sub> and V<sub>OH</sub> are

| (A) 0.8 V and 2.0 V. | <b>(B)</b> 0 V and 5 V.     |

|----------------------|-----------------------------|

| (C) 0.4 V and 2 V.   | <b>(D)</b> 0.4 V and 2.4 V. |

Ans: D

$$V_{OL} = 0.4 V \& V_{OL} = 0.4 \& V_{OH} = 2.4 V$$

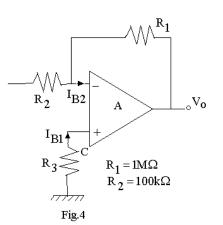

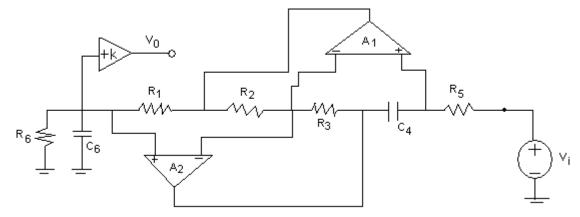

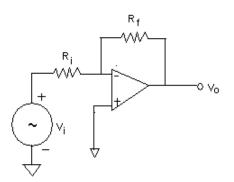

Q.24 An op amp with input offset voltage  $V_{i0} = 0$  is used in the circuit shown in Fig.4. If the input bias currents  $I_{B1} = I_{B2} = 100$  nA then the value of Resistance  $R_3$ , such that the output voltage is zero for zero input voltage, is (A)  $100k\Omega$ **(B)** 1MΩ (C)  $110k\Omega$ **(D)** 90.9kΩ

Ans: D

$R_3 = 90.91 \text{ k} (R_1 11 R_2)$

- (A) Sample time is much smaller than hold time.

- (B) Aperture time is the delay between the time that the pulse is applied to the switch and the actual time the switch closes.

- (C) Acquisition time is the time it takes for the capacitor to charge from one voltage to another voltage.

- (D) The voltage across the hold capacitor changes by 50% during hold time.

ANALOG & DIGITAL ELE

| <u>AE09</u> |                                                                                                                                                                                                                                                         | ANALOG & DIGITAL ELE                                                                                                  |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

|             | Ans: A                                                                                                                                                                                                                                                  | ALL                                                                               |

| Q.26        | The voltage between the emitter and o<br>biased to be at the edge of saturation is<br>(A) 5 volts.<br>(C) 0.1 volts.                                                                                                                                    | ANALOG & DIGITAL ELE<br>collector of a silicon transistor when the transistor<br>:<br>(B) 10 volts.<br>(D) 0.3 volts. |

|             | Ans: D<br>$V_{EOS} = 0.3V$                                                                                                                                                                                                                              |                                                                                                                       |

| Q.27        | The fastest switching logic family is<br>(A) CMOS.<br>(C) DTL.                                                                                                                                                                                          | (B) TTL.<br>(D) ECL.                                                                                                  |

|             | Ans: D                                                                                                                                                                                                                                                  |                                                                                                                       |

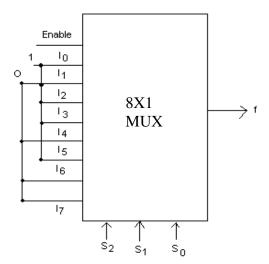

| Q.28        | <ul> <li>A 32 to 1 multiplexer has the following</li> <li>(A) 32 outputs, one input and 5 cont</li> <li>(B) 32 inputs, one output and 5 cont</li> <li>(C) 5 inputs, one control signal and</li> <li>(D) 5 inputs 32 control signals and cont</li> </ul> | trol signals<br>trol signals<br>32 outputs                                                                            |

|             | Ans: B                                                                                                                                                                                                                                                  |                                                                                                                       |

| Q.29        | <ul> <li>The unity gain bandwidth of 741 OPAN</li> <li>(A) 4 MHz.</li> <li>(D) 6 MHz.</li> <li>Ans: D</li> </ul>                                                                                                                                        | MP is typically<br>(B) 2 MHz.<br>(D) 1 MHz.                                                                           |

| Q.30        | <ul><li>The conversion time of a dual-slope AI</li><li>(A) 5 to 10 ns.</li><li>(C) 100 to 200 ns.</li></ul>                                                                                                                                             | <ul> <li>DC is typically in the range of</li> <li>(B) 10 to 100 ns.</li> <li>(D) 2 to 3 ns.</li> </ul>                |

|             | <b>Ans: C</b><br>In dual slope low conversion time is no                                                                                                                                                                                                | ot the primary concern.                                                                                               |

| Q.31        | In a transistor switch, the voltage of accomplish the switching is only about (A) 0.2 V.<br>(C) 0.1 V.                                                                                                                                                  | <ul> <li>(B) 0.4 V.</li> <li>(D) 0.5 V.</li> </ul>                                                                    |

|             | <b>Ans: D</b> 0.5 V assuming silicon transistors.                                                                                                                                                                                                       |                                                                                                                       |

| Q.32        | <ul><li>Worst case ECL noise margins are appr</li><li>(A) 100 mV.</li><li>(C) 250 mV.</li></ul>                                                                                                                                                         | roximately<br>(B) 50 mV.<br>(D) 400 mV.                                                                               |

|             | Ans: C                                                                                                                                                                                                                                                  |                                                                                                                       |

Noise margin = 250 mv.

| <u>AE09</u> |                                                                                                                                                                          | ANALOG & DIGITAL ELE                                                                                                                |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| Q.33        | A certain multiplexer can s<br>inputs does this MUX have?<br>(A) 30 data inputs & 5 se<br>(B) 32 data inputs and 4<br>(C) 32 data inputs and 5<br>(D) None of the above. | ANALOG & DIGITAL ELE<br>witch one of 32 data inputs to its output. How many a<br>elect inputs.<br>select inputs.<br>select inputs.  |

|             | <b>Ans: C</b> 32 data inputs and 5 select in                                                                                                                             |                                                                                                                                     |

| Q.34        | -                                                                                                                                                                        | will always set 'Q' upon the occurrence of the active clock                                                                         |

|             | transition?<br>(A) J = 0, K = 0<br>(C) J = 1, K = 0                                                                                                                      | (B) $J = 1, K = 1$<br>(D) $J = 0, K = 1$                                                                                            |

|             | Ans: C                                                                                                                                                                   |                                                                                                                                     |

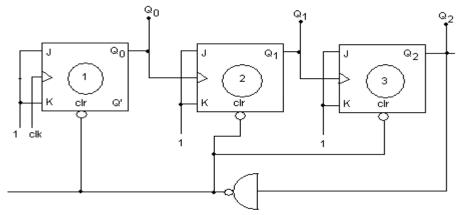

| Q.35        |                                                                                                                                                                          | nter using J-K flip-flops. If the clock frequency to the counter is<br>juency of the counter will be<br>(B) 30 KHz.<br>(D) 3.2 KHz. |

|             | Ans: C<br>2.14 KHz as clock frequency                                                                                                                                    | y gets divided by $n (n = no of mod)$ .                                                                                             |

| Q.36        | The open-loop voltage gain<br>(A) 40 dB.<br>(C) 100 dB.                                                                                                                  | of 741 OPAMP is typically<br>(B) 200 dB.<br>(D) 70 dB.                                                                              |

|             | <b>Ans: C</b> Open loop gain $\approx 10^5$ (20 lo                                                                                                                       | $\log 10^5 = 100 \text{ dB}$ )                                                                                                      |

| Q.37        | How many comparators wou<br>(A) 4000<br>(C) 4095                                                                                                                         | uld a 12-bit flash ADC require?<br>(B) 3095<br>(D) 2512                                                                             |

|             |                                                                                                                                                                          | ors for 12 bit flash ADC<br>= $2^{n}$ -1<br>= $2^{12}$ -1<br>=4095                                                                  |

| Q.38        |                                                                                                                                                                          | opagation delay time of the order of                                                                                                |

| 2.50        | (A) 6 ns.<br>(C) 2 ns.                                                                                                                                                   | (B) 5 ns.<br>(D) 8 ns.                                                                                                              |

removed in schottky transistor.

Q.39 The number of flip-flops required to construct a MOD-10 counter that counts from zero through decimal '0' is

| ( <b>A</b> ) 8.  | <b>(B)</b> 1 | 6. |

|------------------|--------------|----|

| ( <b>C</b> ) 32. | <b>(D)</b> 4 | ŀ. |

#### Ans: D

ANALOG & DIGITAL ELE 4 flip-To construct Mod-10 counter it requires to count from 0000 to 1001(9). Thus for 4 bits, 4 flipflops are required.

- **Q.40** MOSRAMS are available with around

- (A) 1024 memory cells. (B) 4096 memory cells.

- (D) 800 memory cells. (C) zero memory cells.

#### Ans: B

Very popular SRAM. MOS memory chip is 2114 having 4096 bits.

**Q.41** A typical value of the output resistance at room temperature for the 741 OPAMP is (A)  $2M\Omega$ . **(B)** 20KΩ. **(C)** 75Ω. **(D)** 300Ω.

#### Ans: C

Q.42 If the OPAMP specifications lists the input offset voltage as 1.2 mV, then for the circuit shown in Fig.1, the output offset voltage is

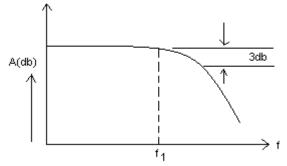

- **Q.43** In a first-order high-pass active filter, if the values of the resistance and the capacitance used are 2.1 K $\Omega$  and 0.05 $\mu$ F respectively, then the cut-off frequency of the filter is equal to

- (A) 15 KHz. **(B)** 1.5 KHz. (C) 3.5 KHz. (D) 0.95 KHz

Ans: B  $f_c = 1.5 KHz$  as  $f_c = 1/2\pi RC$

**Q.44** For a counter-type ADC, if the conversion time is around 4.1 ms then the minimum number of conversions that could be carried out each second would be approximately

| (A) 150 per second. | <b>(B)</b> 244 per second. |

|---------------------|----------------------------|

| (C) 90 per second.  | <b>(D)</b> 209 per second. |

#### Ans: B

as conversion time =  $\frac{1}{f} * (2^n - 1)$

**Q.45** Typical propagation delay of a CMOS gate ranges from  $(\Lambda)$  2 to 15 ns (**B**) 25 to 150 ns

> www.StudentBounty.com nework Help & Pastpapers

| <u>AE09</u> |                                                                                                                | ANALOG & DIGITAL ELE                                                                                                                                                                                           |

|-------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | ( <b>C</b> ) 100 to 200 ns.                                                                                    | ANALOG & DIGITAL ELE.<br>(D) 80 to 120 ns.<br>operate a 2K × 8-bit RAM are:<br>(B) 25<br>(D) 11                                                                                                                |

|             | Ans: A                                                                                                         | Entr                                                                                                                                                                                                           |

| Q.46        | The number of address bits needed to o                                                                         | operate a 2K × 8-bit RAM are:                                                                                                                                                                                  |

|             | (A) 9<br>(C) 15                                                                                                | (B) 25<br>(D) 11                                                                                                                                                                                               |

|             | Ans: D                                                                                                         |                                                                                                                                                                                                                |

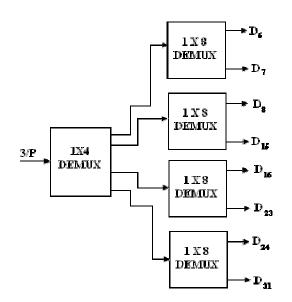

| Q.47        | A one-to-sixteen demultiplexer require                                                                         |                                                                                                                                                                                                                |

|             | <ul><li>(A) 2 select input lines.</li><li>(C) 8 select input lines.</li></ul>                                  | <ul><li>(B) 3 select input lines.</li><li>(D) 4 select input lines.</li></ul>                                                                                                                                  |

|             | <b>Ans: D</b><br>As $1*16$ Demux requires $4(2^4 - 16)$ se                                                     | elect lines to select one among the 16 outputs.                                                                                                                                                                |

|             | - · · · ·                                                                                                      |                                                                                                                                                                                                                |

| Q.48        | <ul><li>The charge coupled devices are impler</li><li>(A) CMOS Technology</li><li>(C) MOS Technology</li></ul> | <ul> <li>(B) PMOS Technology</li> <li>(D) NMOS Technology</li> </ul>                                                                                                                                           |

|             | Ans: C                                                                                                         |                                                                                                                                                                                                                |

| Q.49        | <ul><li>Schottky diodes exhibit a storage time</li><li>(A) Zero sec.</li><li>(C) 30 ns.</li></ul>              | <ul> <li>e of approximately</li> <li>(B) 20 sec.</li> <li>(D) 32 ms.</li> </ul>                                                                                                                                |

|             |                                                                                                                | <b>(D)</b> 52 ms.                                                                                                                                                                                              |

|             | Ans: C<br>30ns storage time is reduced due to me                                                               | etal-semiconductor junction.                                                                                                                                                                                   |

| Q.50        | In an analog multiplier, if both the inp<br>to be                                                              | puts are positive or negative then the multiplier is said                                                                                                                                                      |

|             | <ul><li>(A) a two quadrant multiplier.</li><li>(C) a four quadrant multiplier.</li></ul>                       | <ul><li>(B) a one quadrant multiplier.</li><li>(D) a three quadrant multiplier.</li></ul>                                                                                                                      |

|             | Ans: C                                                                                                         |                                                                                                                                                                                                                |

| Q.51        | <ul><li>The large signal differential voltage an</li><li>(A) 100 V/mv.</li><li>(C) 1000 V/mv.</li></ul>        | <ul> <li>mplification of the 741 OPAMP is typically about</li> <li>(B) 500 V/mv.</li> <li>(D) 200 V/mv.</li> </ul>                                                                                             |

|             | Ans: C<br>as Gain-Bandwidth product= 1 MHz                                                                     |                                                                                                                                                                                                                |

| Q.52        |                                                                                                                | <ul> <li>arage input bias current for an OPAMP are respectively</li> <li>arrents at each input of the OPAMP are respectively</li> <li>(B) 22.5 nA &amp; 30.2 nA.</li> <li>(D) 2.5 nA &amp; 3.02 nA.</li> </ul> |

|             | Ans: A                                                                                                         |                                                                                                                                                                                                                |

|             |                                                                                                                |                                                                                                                                                                                                                |

www.StudentBounty.com Homework Help & Pastpapers

$I_B^{+} - I_B^{-} = |I_{0s}|$  offset current = 5nA Bias current = 30nA  $I_B^{+} + I_B^{-} = I_{Bavg}$

Thus input bias current at each input solving above two equations gives Ans (A)

ANALOG & DIGITAL ELE (A) (A) (A) Q.53 In a first-order low-pass active filter, if the values of the resistance and the capacitor used are 1.2 K $\Omega$  and 0.02µF respectively, then the cut-off frequency of the filter is

(B) 8.7 KHz. (A) 3.6 KHz. (C) 8.2 Hz. (D) 6.63 KHz.

Ans: D As  $f_c = \frac{1}{2\pi RC}$

- Q.54 A clock rate of one megahertz operating a 12-stage counter of a counter-type ADC would need a maximum conversion time of approximately

- (A) 3.2 ms. **(B)** 4.1 ms. (C) 8 ms. (D) 7.1 ms.

#### Ans: A

Conversion time =

$$\frac{1}{f} \times (2^n - 1)$$

$$N = 12$$

,  $f = 1MHz$

0.55 Typical propagation delay of an ECL circuit is (A) 10 ns. **(B)** 5 ns. (**C**) 1 ns. **(D)** 3.2 ns.

#### Ans: B

5 ns – fastest logic family.

Q.56 The number of states in its counting sequence that a ring counter consisting of 'n' flip-flops can have is

| <b>(A)</b> $2^n - 1$ | <b>(B)</b> $2^{n-1}$ |

|----------------------|----------------------|

| ( <b>C</b> ) n       | <b>(D)</b> $2^{n+1}$ |

#### Ans: C

n bit shift register connected as ring counter can count total N-states.

**Q.57** The number of select input lines required by a 1-to-8 demultiplexer are

| ( <b>A</b> ) Two. | <b>(B)</b> One.     |

|-------------------|---------------------|

| (C) Four.         | ( <b>D</b> ) Three. |

#### Ans: D

1 to 8 Demux require 3  $(8=2^3)$  select lines to select one output among 8.

Q.58 The Maximum binary number counted by a ripple counter that uses four FlipFlop's is (A)  $(0000)_2$ **(B)**  $(1011)_2$ (C)  $(1111)_2$ **(D)**  $(0101)_2$

#### www.StudentBounty.com ework Help & Pastpapers

#### Ans: C

as ripple counter with four FF's will count 16 states from zero to fifteen.

- ANALOG & DIGITAL ELE 'o fifteen. Q.59 The cut-in voltage of the aluminium n-type Schottky diode is about (A) 0.5 V. **(B)** 0.5 μV.

- (C) 0.35 V.

**(D)** 0.35 mV.

#### Ans: C

as the cut in voltage becomes half due to metal – sc function.

#### **State True or False**

**Q.60** The amplifiers in the sample and hold circuit are used to provide voltage amplification. (A) True (B) False

#### Ans: B

Sample and hold circuit does not have amplifiers.

- Q.61 In a Chebyshev filter of odd order, the oscillatory curve of the magnitude response does not start from unity

- (A) True (B) False

#### Ans: B

As the magnitude response starts from unity in chebyshev odd order filters.

Q.62 Due to its simple circuit structure, MOS circuitry is not so well suited for LSI (B) False (A) True

#### Ans: B

**Q.63** The bit storage cells in a RAM, when high speed is required make use of a BJT

#### (**B**) False (A) True

#### Ans: A

True as switching speed of BJT is high.

**Q.64** An instrumentation amplifier should not have a high CMRR (A) True (B) False

#### Ans: B

Instrumentation Amplifier amplifies the difference of the I/P signal.

**Q.65** In a Chebyshev filter of even order, the oscillatory curve of the magnitude response starts from unity (A) True (B) False

#### Ans: B

Magnitude response of even order Chebyshev filter does not start from unity.

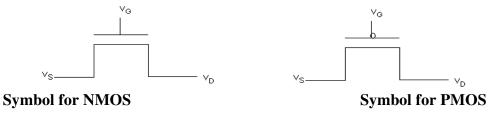

**Q.66** As the gate voltage switches from a LOW voltage to a HIGH voltage, the N-MOSFET will switch from a very I OW resistance to a HIGH resistance

#### www.StudentBounty.com nework Help & Pastpap

(A) True

(**B**) False

#### Ans: B

ANALOG & DIGITAL ELE As the gate voltage switches from low voltage to high voltage. NMOS starts conducting and it will switch from very high resistance to low resistance.

**Q.67** The circuit for a DEMUX is basically the same as for a decoder, provided the decoder has an enable input

> (A) True (**B**) False

#### Ans: A

DEMUX & Decoder are same circuits with decoder has an enable input.

#### PART – II

## DESCRIPTIVES

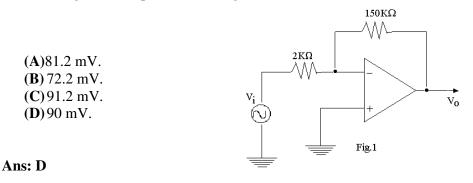

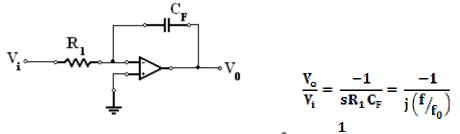

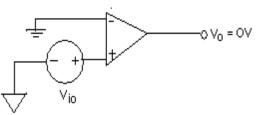

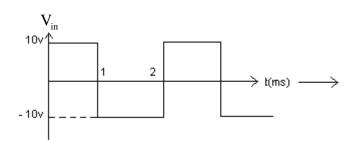

StudentBounty.com Q.1 Explain Miller Integrator. What are the effects of the OP-AMP input offset voltage, input bias and offset currents on the performance of Miller Integrator.

Ans:

The circuit shown realizes the mathematical operation of integration. Writing modal equation at node (1)

$$\frac{v_i}{R_1} + C_1 \frac{dv_o}{dt} = o \quad or \quad \frac{dv_o}{dt} = -\frac{1}{R_1 C_1} v_i$$

Integrating both sides

$$\int_{0}^{t} dv_{o} = -\frac{1}{R_{1}C_{1}} \int_{0}^{t} v_{i} dt$$

$$v_{o}(t) = -\frac{1}{R_{1}C_{1}} \int_{0}^{t} v_{i}(t) dt + v_{o}(0)$$

Where  $v_0(0)$  is the initial voltage on  $C_1$  therefore this is initial output voltage.

This circuit provides an output voltage that is proportional to integration of the input voltage with  $v_0$  being the initial condition of integration and  $C_1R_1$  the integration time constant.

When  $v_i = 0$  the above integrator works as an open loop amplifier. This is because the capacitor  $C_1$  acts as an open circuit  $(X_{C1=} \infty)$  to the input offset voltage  $v_{io}$ . Thus the input offset voltage  $v_{io}$  and the part of input current charging capacitor  $C_1$  produces the error voltage at the output of the integrator. Therefore, in the practical integrator to reduce the error voltage at the output, a resistor  $R_F$  is connected in parallel to capacitor  $C_1$ .

Q.2 What is a counter? How are counters broadly classified? Write at least two lines on each such classification. (7)

#### Ans:

A sequential circuit that goes through a prescribed set of states upon application of input pulses is called a counter.

#### **Types of Counters**

(i) Ripple Counters

#### www.StudentBounty.com lomework Help & Pastpa

#### ANALOG & DIGITAL EN

- Binary

- BCD

- (ii) Synchronous Counters

- Binary

- BCD

- (iii)Ring Counter

StudentBounty.com Ripple counters are those, in which the change in output of one counter flip flop triggers the next flip flop which further triggers the next one, thus the effect of input pulses is rippled through. Binary counters of this type cycle through the various binary codes.

BCD counters on the other hand cycle through the BCD code. Synchronous counters act so that a common clock pulse triggers all the flip flops at once. The ripple effect is not observed and all flip-flops flip or flop simultaneously. Here also the Binary and BCD code cycle through in the corresponding counters. In a ring counter, only one bit is high at a time and the counters are connected in a loop. Thus a k flip flop ring counter has k states.

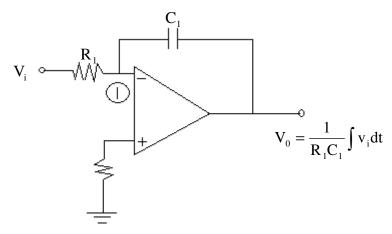

0.3 Draw the circuit diagram of two stage CMOS op-amp configuration. What do you understand by systematic output dc offset voltage? How can it be eliminated? (8)

Ans:

Unless properly designed, this CMOS OPAMP circuit exhibits a type of input offset voltage that can be present even if all appropriate devices are perfectly matched. This predictable systematic offset voltage at input causes systematic output offset voltage.

It can be eliminated by sizing the transistors so as to satisfy following constraint:

$$\frac{(W/L)_{6}}{(W/L)_{4}} = \frac{(W/L)_{7} \times 2}{(W/L)_{5}}$$

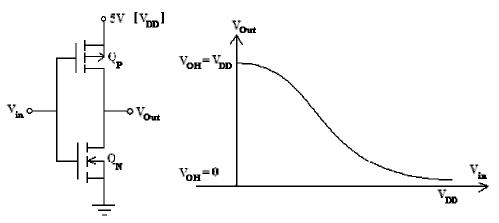

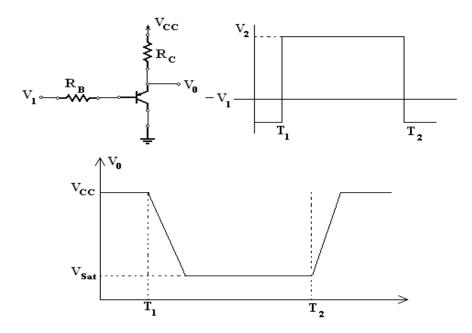

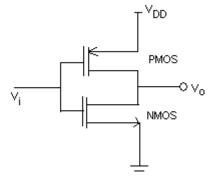

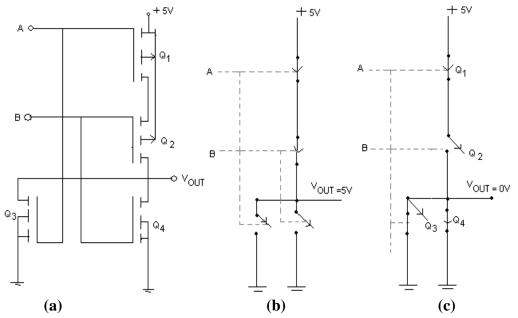

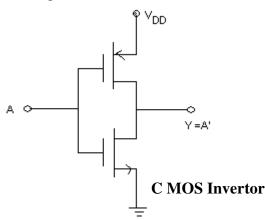

0.4 Draw the circuit diagram of a CMOS inverter and explain its operation. (6)

#### Ans:

**CMOS Inverter**: It is most widely used in chip design. This operates with very little power loss. CMOS inverter has good logic buffer characteristics as its noise margin in both low and high states are large. CMOS does not contain any resistors which makes it more power

#### www.StudentBounty.com nework Help & Pastpa

### ANALOG & DIGITAL EN

StudentBounts.com efficient. When  $V_{in} = V_{DD}$ ,  $Q_n$  turns on and  $Q_p$  turns off therefore  $V_{out} = 0$  volts (1 since transistors are connected in series, the current  $I_D$  is very small. When  $V_{in} = 0V$ on and  $Q_n$  turns off and  $V_{out} = V_{DD}$  (logic 1). So output is inverted version of input voltage

Transfer characteristic of CMOS inverters.

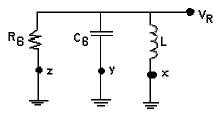

- The transfer function of a two port network is given by  $T(s) = \frac{z_2}{z_1 + z_2}$  where  $z_1$  and  $z_2$ Q.5 represent any impedances. Explain how the following passive filters can be realized from this network.

- (4) a) Bandpass filter.

- b) Notch filter. (5)

- c) All pass filter. (5)

Ans:

1) Putting  $Z_1 = SL_1 + 1/SC_1 \& Z_2 = R_1$

$$T(S) = \frac{R_1}{SL_1 + 1/SC_1 + R_1} = \frac{SC_1R_1}{S^2L_1C_1 + SC_1R_1 + 1} \dots BandPass \ Filter$$

2) Putting  $Z_1 = R_1 \& Z_2 = SL_1 + 1/SC_1$

$$T(S) = \frac{SL_1 + 1/SL_1}{SL_1 + 1/SL_1 + R_1} = \frac{S^2L_1C_1 + 1}{S^2L_1C_1 + SC_1R_1 + 1}$$

.....Notch Filter

3)Transfer function of All pass Filter

$$T(S) = \frac{1 - SRC}{1 + SRC}$$

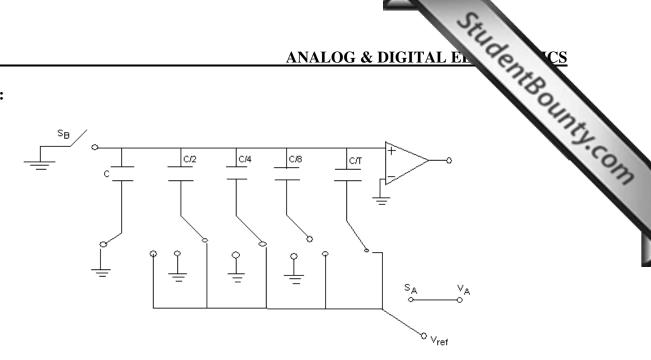

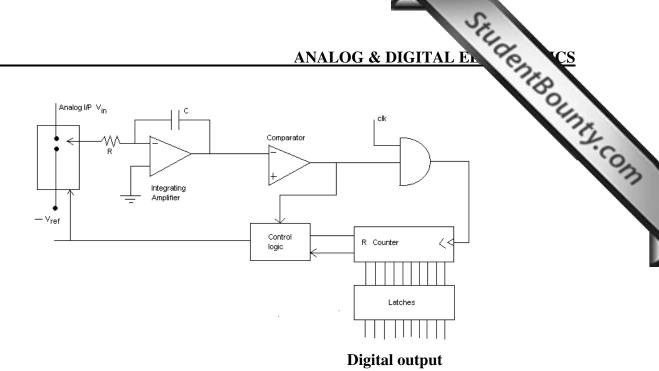

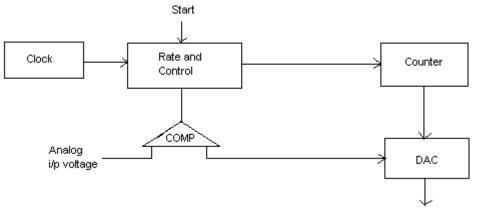

Q.6 With proper diagram explain the operation of dual slope A/D converter and charge redistribution A/D converter. Compare their advantages and disadvantages. (10)

# www.StudentBounty.com

Ans:

The charge redistribution A/D converter utilizes binary weighted capacitor array, a voltage comparator and analog switches; control logic. Capacitor  $C_T$  serves the purpose of terminating the capacitor array making total capacitance of the array equal to desired value of 2C.

The operation has 3 phases: a) Sample phase, b) Hold phase c) Charge- redistribution phase.

- a) Sample phase: In this phase, switch  $S_B$  is closed, thus connecting the top plate of all capacitors to ground and setting V<sub>0</sub> to zero. Meanwhile switch S<sub>A</sub> is connected to analog input voltage V<sub>A</sub> which appears across all capacitors resulting in a stored charge of 2CV<sub>A</sub>. Thus, a sample of  $V_A$  is taken and a proportionate amount of charge is stored on capacitor array.

- **b)** Hold phase: In this phase, switch  $S_B$  is opened and switches  $S_1$  to  $S_5$  and  $S_T$  are thrown to the ground side. Thus top plates are open circuited while bottom plates are grounded. Since no discharge path is provided, capacitor charges remain constant, with total equal to  $2CV_A$ . So, voltage at top plate becomes -  $V_A$ . Finally  $S_A$  is connected to  $V_{REF}$ .

- c) Charge-redistribution phase: In this phase, switch  $S_1$  is connected to  $V_{REF}$  (through S<sub>A</sub>). The circuit then consists of V<sub>REF</sub>, a series capacitor C and a total capacitance to ground of value C. The capacitive divider cause of a voltage increment of  $V_{REF}/2$  to appear on top plates. None if  $V_A$  is greater then  $V_{REF}/2$ , the net voltage at the top plate will remain negative which means that  $S_1$  will be left in its new position as we move on the switch  $S_2$ . If  $V_A$  was smaller then  $V_{REF}/2$  then the net voltage at the top-plate would become positive. The comparator will detect this situation and signal the control logic to return  $S_1$  to its ground position and then to move on to  $S_2$

Next, switch  $S_2$  is connected to  $V_{REF}$  which causes a voltage increment of  $V_{REF}$  / 4 appear on top plate.

#### ANALOG & DIGITAL EN

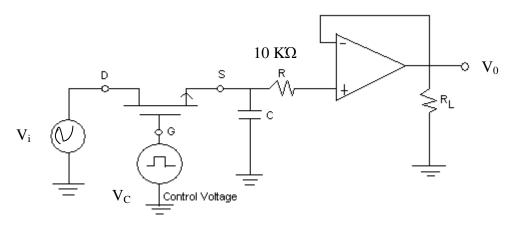

**Q.7** Explain the operation of sample & hold circuit. Discuss its applications. (4)

Ans:

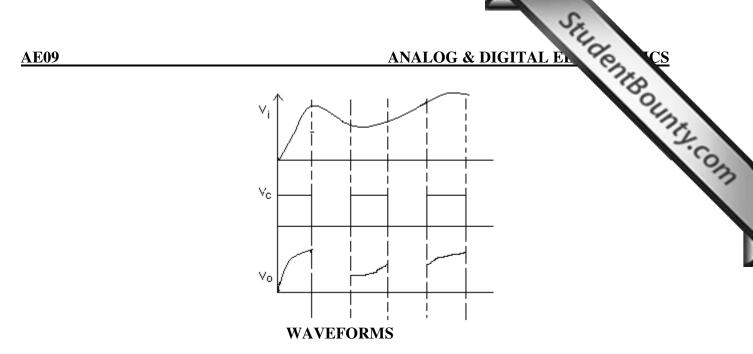

Here, the MOSFET is used as a switch and OPAMP as a buffer. The switch is put on by applying a positive pulse on the gate. The capacitor gets charged with the required value with RC time constant. Sample & hold circuit can be used to produce samples of analog voltage which can be used in a analog to digital converter (ADC). The input voltage  $V_i$  to be sampled is applied at the drain. When control voltage is high MOSFET is ON and capacitor is charged up to the value of input signal, and the same voltage is available at the output. When Vc is zero the MOSFET is OFF and acts as open circuit. The only discharge path of capacitor is through OPAMP. However the input impedance of voltage follower is very high, hence the voltage across capacitor is retained.

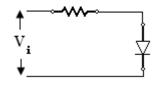

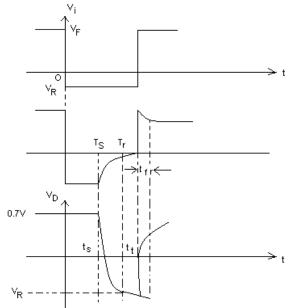

Q.8 What types of doping should be used in a switching diode. What is reverse recovery time? (4)

#### Ans:

In switching diodes a lightly doped neutral region is made whose length is shorter than a minority carrier diffusion length. In this case the stored charge for forward conduction is very small since most of the injected carriers diffuse through the lightly doped region to end contact. When such a diode is switched to reverse conduction, very little time is required to eliminate the stored charge in the narrow neutral region.

A second approach is to add efficient recombination centres to the bulk material. For Si diode, Au doping is useful for this purpose. To a good approximation the carrier the carrier lifetime varies with the reciprocal center concentration.

The total time required for the reverse current to decay to 10% of its maximum magnitude is defined as recovery time.

Q.9 Explain the operation of a MOSFET analog switch with suitable circuit diagram. (6)

#### Ans:

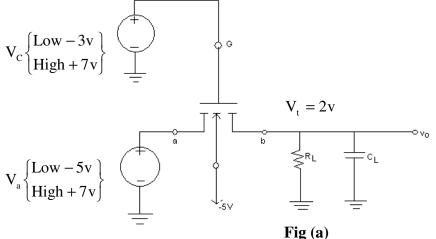

**MOSFET as analog switch**: In applications where need arises to switch analog signal, the switch is said to be analog switch. Following is a circuit of analog switch using N MOS transistor

Let input voltage  $V_A$  be in the range of  $\pm 5V$ . In order to keep the substrate-to-source and substrate-to-drain pn junction reverse biased at all times, the substrate terminal is connected to -5V. The control voltage  $V_c$  is used to turn the switch on and off .Let us assume that the device has a threshold voltage  $V_t=2V$ . Then in order to turn the transistor on for all possible input signal levels the high value of  $V_c$  should be +7V and to turn off transistor for all possible input voltage levels the low value of  $V_c$  should be a maximum of -3V.

MOSFET is a symmetrical device, with the source and the drain interchangeable. The operation of the device as switch is based on this interchangeability of roles. Whichever of the two terminals a and b is at higher voltage acts as the drain. Thus if analog input voltage is positive say +4V then terminal a acts as drain and b as source. Then the circuit takes the form as shown in figure (b) above. The device will operate in triode region and output voltage will be very close to the input analog signal level of +4v.On the other hands if the input signal is negative say -4v then terminal b acts as the drain. The circuit takes the form shown in figure (c). Again device operates in triode region and  $V_0$  will be only slightly higher than analog input signal level of -4V.

Q.10 What property of Schottky diode make it suitable for fast switching? Explain . (4)

#### Ans:

The schottky barrier diode is formed by bringing metal into contact with a moderately doped n-type semiconductor. In schottky diode current is conducted by majority carriers. Thus it does not exhibit the minority-carrier charge storage effect; as a result diodes can be switched on to off vice versa much faster than is possible with p-n junction diode.

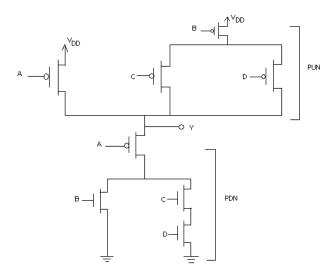

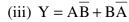

- Q.11 Implement the following Boolean expressions by synthesizing Pull up and Pull down networks:

- (i)  $Y = \overline{AB}$ . (4)

- (ii)  $Y = \overline{A(B + CD)}$ . (5)

- (iii)  $Y = A\overline{B} + \overline{A}B$ . (5)

<u>ANALOG & DI</u>GITAL EL

Ans:

(i)Y =  $\overline{AB}$

StudentBounty.com Pull down network (PDN) can be synthesized by expressing  $\overline{Y}$  as function of u complemented variables. We consider input combination that requires Y to be low.

$$Y = AB$$

$$= \bar{A} + \bar{B}$$

This requires that both A and B to be high. Thus PDN consists of two NMOS transistors in series.

To synthesize Pull up network (PUN), we consider the input combination that result in Y being high. From Y=AB, it requires that for Y to be high, A or B to be low.

(ii) PUN

$$Y = \overline{A(B + CD)}$$

$= \overline{A} + (\overline{B} + \overline{CD})$

$= \overline{A} + (\overline{B} \cdot \overline{CD})$

$= \overline{A} + \overline{B} \cdot (\overline{C} \cdot \overline{D})$

$= \overline{A} + \overline{B} \cdot (\overline{C} + \overline{D}),$

Y is high for A low or B low and either C or D low.

$PUN$

$A \rightarrow O$

$A \rightarrow O$

PDN

$$Y = \overline{A(B + (D))}$$

For Y to be low, A should be high and simultaneously either B high or C and D both high.

www.StudentBounty.com

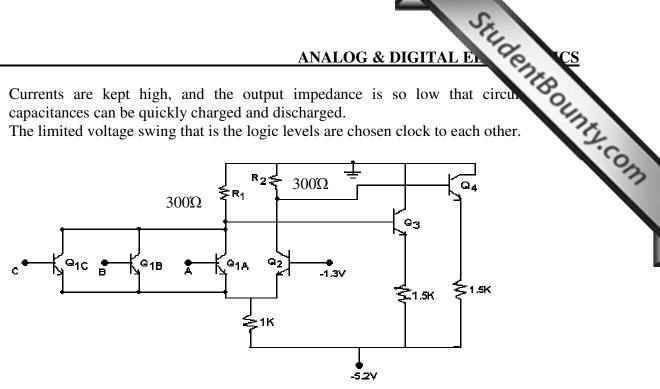

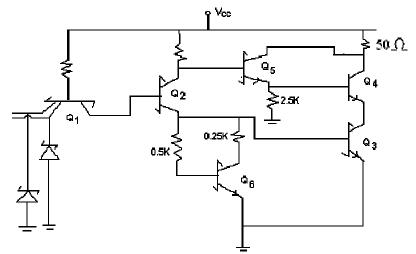

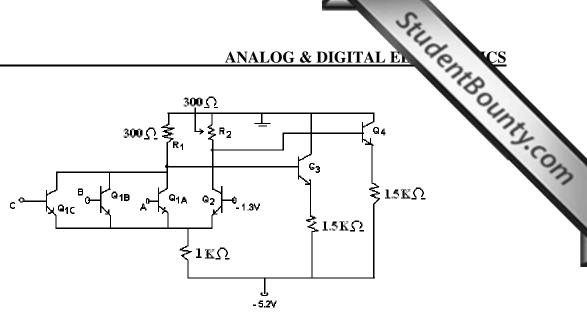

Q.12 Explain the following logic families and compare their performances. (9) (i) ECL. (ii) TTL

#### Ans:

(i)ECL (Emitter Coupled Logic) is recommended in high frequency applications where its speed is superior.

#### Justification:

- 1. It is non saturated logic, in the sense that transistors are not allowed to go into saturation. So, storage time delays are eliminated and therefore the speed of operation is increased.

- 2. Currents are kept high, and the output impedance is so low that circuit and stray capacitances can be quickly charged and discharged.

- 3. The limited voltage swing. (i.e. the logic levels are chosen close to each other)

#### **Important features:**

- 1. One advantage of differential input try in ECL gates is that it provides common mode rejection power supply noise common to both sides of the differential configuration is effectively cancelled out.

- 2. Also, since the ECL output is produced at an emitter follower, the output impedance is desirably low. As a consequence, the ECL gates not only have a larger fan out but also are relatively unaffected by capacitive loads.

(ii) TTL stands for "Transistor – Transistor Logic". It is the most popular logic family and also the most widely used bipolar digital IC family. It uses transistors operating in saturated mode. Good speed, low manufacturing cost, wide range of circuits and availability in SSI and MSI are its merits.

The open collector arrangement is much slower than the totem pole arrangement, because the time constant with which the load capacitance charges in this case is considerably larger. (In the case of totem pole output, it is active pull up. Thus the output rises fast). For this reason, the open collector circuits should not be used in applications where switching speed is a principal consideration.

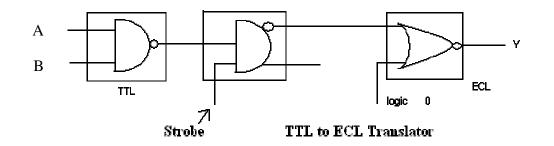

Q.13 How ECL and TTL logic families are interfaced with each other. (

(5)

#### Ans:

ANALOG & DIGITAL EL "veen TTL and ECL g "al shifting circuit "TL, two lev Interfacing of ECL and TTL with each other: In interfacing between TTL and ECL logic levels between two systems are entirely different therefore level shifting circuit required to be used between these gates. For TTL to ECL and ECL to TTL, two le translator IC's are available-MC 10 H124.

The logic levels of translator circuit are

$V_{IH} = 2V, V_{IL} = 0.8V$

$V_{OH} = -0.98 \text{ v}, V_{OL} = -1.63 \text{ V}$

For TTL IC we have  $V_{OH} = 2.4V$  and  $V_{OL} = 0.4V$ . Comparing the O/P logic levels of TTL and I/P logic levels of translator IC we find

$V_{IH}$  (Translator) <  $V_{OH}$  (TTL)

$V_{IL}$  (Translator) >  $V_{OL}$  (TTL)

This shows that the I/P logic levels of translator are compatible with the O/P logic levels of TTL

Similarly

$V_{IH}$  (ECL) <  $V_{OH}$  (Translator)  $V_{IL}$  (ECL) >  $V_{OL}$  (TTL)

www.StudentBounty.com Homework Help & Pastpapers

#### <u>ANALOG</u> & DIGITAL EX

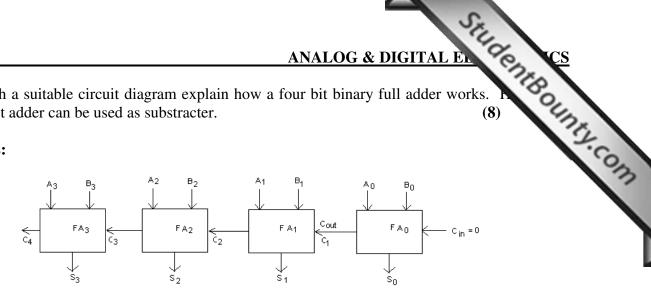

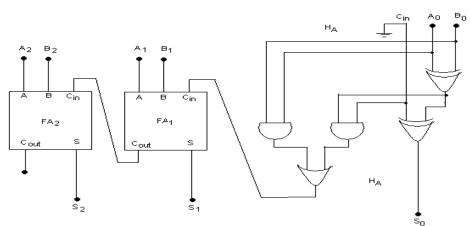

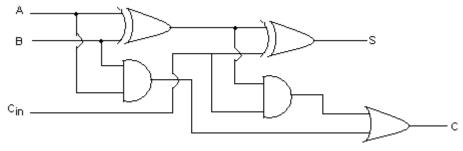

With a suitable circuit diagram explain how a four bit binary full adder works. **0.14** 4-bit adder can be used as substracter.

Ans:

#### 4 bit Adder

**Operation:** The first  $FA_0$  adding the LSB,  $A_0$  and  $B_0$  is essentially a half adder whose sum bit is  $A_0 \oplus B_0$  and  $C_{out}=A_0B_0$  since  $C_{in}$  is set to 0. The  $C_{out}$  of the addition of LSB's is carried over to the addition of next bits i.e.A<sub>1</sub>,B<sub>1</sub> which are added using a full adder, FA<sub>1</sub> This procedure continues with all the next adders being full adders till the MSB's,  $A_3$  and  $B_3$ . The final sum is  $S_3S_2S_1S_0$  where  $S_3$  is the MSB and  $S_0$  is the LSB.

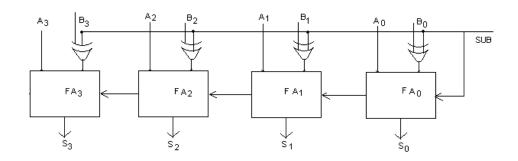

#### **4 bit Subtractor**

The subtraction is performed using two's complement as A+B+1. If B=1, then Output of XOR gate is 0. If B=0, then output is 1. Thus a four bit adder is converted into a subtractor by connecting bits of input number B as one of the input of XOR gate. The second input of XOR gate is kept as logic 1. Now when I/P B=0 then output of XOR gate is 1 and if B=1 then output is 0. Now 1 is added to this complimented number so that we get B+1. These input's are applied to the B input of the adder and at the output, we will get the output as A + B + 1

**Q.15** Explain the operation of a BCD to decimal decoder. (6)

#### Ans:

**BCD to Decimal Decoder** This is a type of decoder which decodes the BCD input in decimal. There are four input's and ten output's and depending on the input combinations the corresponding output line is high.

#### **AE09**

www.StudentBounty.com

ANALOG & DIGITAL EF

|         |    |                       | ₩→<br>×→<br>×→ |                | 0 Decimal<br>:coder | $ \xrightarrow{P_0} \stackrel{D_0}{\rightarrow} \stackrel{D_1}{\rightarrow} \stackrel{D_2}{\rightarrow} $ |                |       |                | .0        |

|---------|----|-----------------------|----------------|----------------|---------------------|-----------------------------------------------------------------------------------------------------------|----------------|-------|----------------|-----------|

|         |    |                       | z →            |                |                     | →Dg                                                                                                       |                |       |                |           |

| WXYZ    | Do | <b>D</b> <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> | $D_4$               | D5                                                                                                        | D <sub>6</sub> | $D_7$ | D <sub>8</sub> | <u>D9</u> |

| 0 0 0 0 | 1  | 0                     | 0              | 0              | 0                   | 0                                                                                                         | 0              | 0     | 0              | 0         |

| 0 0 0 1 | 0  | 1                     | 0              | 0              | 0                   | 0                                                                                                         | 0              | 0     | 0              | 0         |

| 0 0 1 0 | 0  | 0                     | 1              | 0              | 0                   | 0                                                                                                         | 0              | 0     | 0              | 0         |

| 0 0 1 1 | 0  | 0                     | 0              | 1              | 0                   | 0                                                                                                         | 0              | 0     | 0              | 0         |

| 0 1 0 0 | 0  | 0                     | 0              | 0              | 1                   | 0                                                                                                         | 0              | 0     | 0              | 0         |

| 0 1 0 1 | 0  | 0                     | 0              | 0              | 0                   | 1                                                                                                         | 0              | 0     | 0              | 0         |

| 0 1 1 0 | 0  | 0                     | 0              | 0              | 0                   | 0                                                                                                         | 1              | 0     | 0              | 0         |

| 0 1 1 1 | 0  | 0                     | 0              | 0              | 0                   | 0                                                                                                         | 0              | 1     | 0              | 0         |

| 1 0 0 0 | 0  | 0                     | 0              | 0              | 0                   | 0                                                                                                         | 0              | 0     | 1              | 0         |

| 1 0 0 1 | 0  | 0                     | 0              | 0              | 0                   | 0                                                                                                         | 0              | 0     | 0              | 1         |

Now Ten K- maps are required to get the ten outputs from  $D_0$  to  $D_9$ . Instead of making ten Kmaps, we make only one K-map and make the entries as follows:

| wx/yz | 00 | 01 | :1 | 10 |  |

|-------|----|----|----|----|--|

| 00    | Do | Dı | Ds | Da |  |

| 01    | D4 | Dø | D7 | D. |  |

| 11    | ×  | x  | x  | x  |  |

| 10    | Da | D9 | x  | x  |  |

While solving for  $D_0$  consider  $D_0$  as high and all other D's as zero. Some of the functions are  $D_0 = w'x'y'z'$   $D_1 = w'x'y'z$

$D_2 = x'yz'$  (by combining with don't care at 1010)

- $D_3 = x'yz$  (by combining with don't care at 1011)

- $D_4 = xy'z'$

$D_5 = xy'z$

#### www.StudentBounty.com Homework Help & Pastpapers

#### Ans:

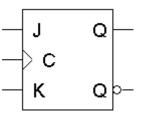

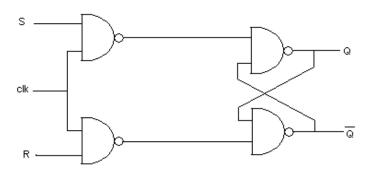

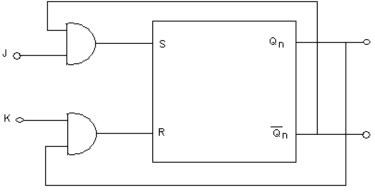

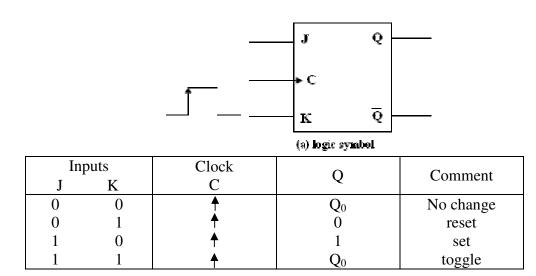

(i) JK Flip-flop: JK flip flop is a single bit storage device which came into the picture to overcome the disadvantages of RS flip flop. This disadvantage was Race-around condition. The following excitation table shows what flip-flop inputs are required in order to make a desired state change.

| Q(t) | Q(t+1) | J | K | Operation        |

|------|--------|---|---|------------------|

| 0    | 0      | 0 | Х | No change/reset  |

| 0    | 1      | 1 | Х | Set/complement   |

| 1    | 0      | X | 1 | Reset/complement |

| 1    | 1      | X | 0 | No change/set    |

| Truth Table |                      |       |            |  |  |  |  |

|-------------|----------------------|-------|------------|--|--|--|--|

| J           | J K Q(t+1) Operation |       |            |  |  |  |  |

| 0           | 0                    | Q(t)  | No change  |  |  |  |  |

| 0           | 1                    | 0     | Reset      |  |  |  |  |

| 1           | 0                    | 1     | Set        |  |  |  |  |

| 1           | 1                    | Q'(t) | Complement |  |  |  |  |

#### Logic Symbol

JK flip-flops are good because there are many don't care values in the flip-flop inputs, which can lead to a simpler circuit.

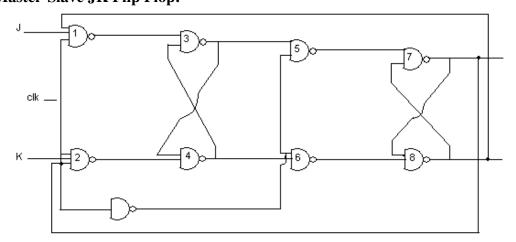

**Circuit of JK Flip Flop**

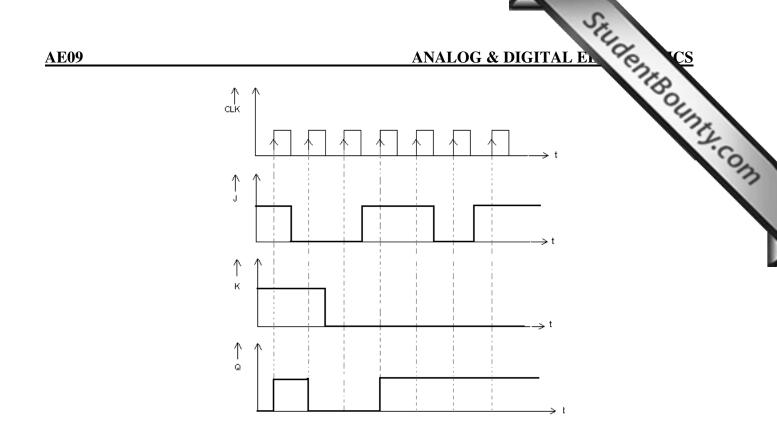

Example waveforms for J K Flip Flop

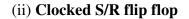

Circuit of SR flip flop

#### Characteristic table

| clk | S | R | $Q_{t+1}$ |               |

|-----|---|---|-----------|---------------|

| 0   | Х | Х | Qt        | No Change     |

| 1   | 0 | 0 | Qt        | No Change     |

| 1   | 0 | 1 | 0         |               |

| 1   | 1 | 0 | 1         |               |

| 1   | 1 | 1 |           | Forbidden (?) |

There are two inputs S(Set) and R (Reset). When clock is enabled (clk=1) and both the inputs are 0 then flip flop does not change the state. S=1 and R=0 sets the Q output, whereas S=0,

R=1 resets Q output. S=R=1 input condition is forbidden as both output Q and Q will try to become 1. This is regarded as invalid circuit operation. when clk = 0 output will always retain the previous state.

#### Characteristic equation for RS flip flop is

Timing wave form for SR flip-flop

- Q.17 Write short notes on any **TWO** of the following:

- (i) RAM & PROM.

- (ii) Seven segment display system.

- (iii) Shift register.

#### Ans:

#### (i) RAM and PROM

A memory unit is a collection of storage cells together with associated circuits needed to transfer information in and out of the device. The time it takes to transfer information to or from any desired random location is always same, hence the name **RAM**(Random Access Memory). It is used for storing temporary data as it is volatile. The variables required for a particular program are stored. Here RAM can perform both read and write operations. Therefore all the variables during the ALF are stored here. The static RAM (SRAM) consists of internal latches that store the binary information. The stored information remains valid as long as power is there. The dynamic RAM stores information in the form of charges on capacitor. The capacitors are provided inside the chip by MOS transistors. The stored charge tends to get discharged with time and the charge has to be periodically refreshed.

(7+7)

DRAM offers reduced power consumption and larger storage capacity in a single memory chip. SRAM is easier to use and has shorter read and write cycles.

When production in small quantities is required a PROM or programmable read only memory is used. When ordered PROM units contain all the fuses intact giving all 1's in the bits of stored words. The fuses in PROM are blown using application of a high voltage pulse to the device through a special pin. A blown fuse gives a binary '0' state. This allows the user to program it in the lab. Special programmes are used for this. The hardware procedure for programming ROMs is irreversible & once programmed the pattern is irreversible. The

omework Help & Pastpap

**ANALOG & DIGITAL EX**

StudentBounty.com EPROM is erasable and can be restructured. When EPROM is placed under special light for a given period of time, the short wave radiations discharge the internal floating But individual bits can't be reprogrammed as in case of EEPROM. The programming tak of time, about 30 min and the whole ROM is reprogrammed. The device has to be remove from its socket to reprogram it.

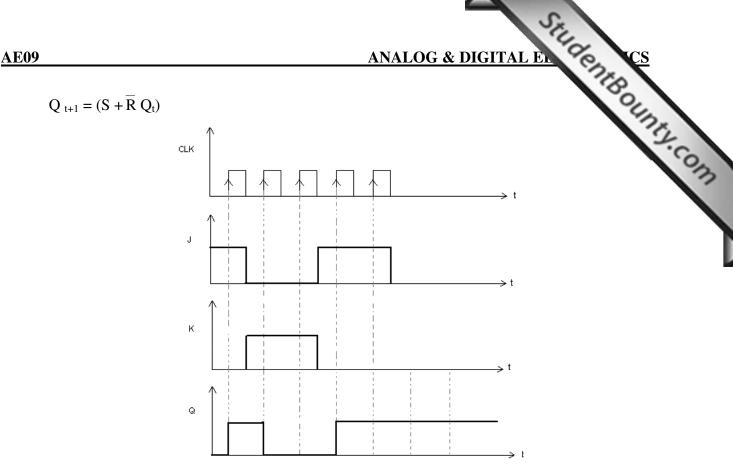

#### (ii) Seven Segment display systems:

This system accepts BCD numbers as input and there are seven outputs which are connected to seven LED's. According to the display required corresponding LED's are made high. For example if 'Two' is to be displayed then a, b, e, d and g should be high and others are keptlow.

| W | Х | Y | Ζ | a | b        | с  | d | e | f | g |

|---|---|---|---|---|----------|----|---|---|---|---|

| 0 | 0 | 0 | 0 | 1 | 1        | 1  | 1 | 1 | 1 | 0 |

| 0 | 0 | 0 | 1 | 0 | 1        | 1  | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 | 1        | 0  | 1 | 1 | 0 | 1 |

| 0 | 0 | 1 | 1 | 1 | 1        | 1  | 1 | 0 | 0 | 1 |

| 0 | 1 | 0 | 0 | 0 | 1        | 1  | 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 | 1 | 0        | 1  | 1 | 0 | 1 | 1 |

| 0 | 1 | 1 | 0 | 1 | 0        | 1  | 1 | 1 | 1 | 1 |

| 0 | 1 | 1 | 1 | 1 | 1        | 1  | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 1        | 1  | 1 | 1 | 1 | 1 |

| 1 | 0 | 0 | 1 | 1 | 1        | 1  | 1 | 0 | 1 | 1 |

|   |   |   |   | Т | ruth tab | 1. |   |   |   |   |

Truth table

www.StudentBounty.com omework Help & Pas

#### **AE09**

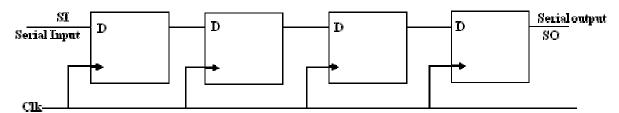

ANALOG & DIGITAL EL ' inations so they can be treat ^ for a, b, c, .... g are st NAND-NAND gat ' of storing on A The input combinations 1010 to 1111 are invalid combinations so they can be treat care conditions while solving the K-maps. Now seven K-maps for a, b, c, .... g are 3 terms of I/P<sup>s</sup> BCD number wxyz and implemented using AND-OR or NAND-NAND gat (iii) Shift Register: A register is a group of flip flops. Each flip flop is capable of storing on bit of information. An n bit register is capable of storing n bite of binary information. A register capable of shifting its binary information in one or both direction is called a shift register. It consists of a chain of flip flops in cascade, with the output of one flip flop connected to the input of the next flip flop. All flip flops receive common clock pulses, which activate the shift from one stage to the next.

This is a 4 bit shift register. The output of a given flip - flop is connected to the D input of the flip – flop at its right. Each clock pulse shifts the contents of the register one bit position to the right. The serial input determines what goes into the left most flip flop during the shift. Serial output is taken from the output of the right most flip flop. This is a right shift operation. We can also construct a left shift register where inputs are inserted from right and output is taken from the left. If the flip flop outputs of a shift register are accessible then information entered serially by shifting can be taken out in parallel manner from the flip flop's. If a parallel load capability is added to shift register then data entered in parallel can be taken out in serial fashion by shifting the data stored in the register.

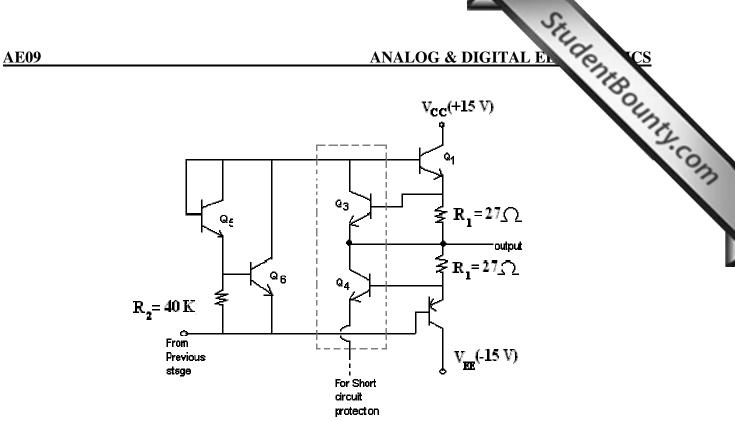

**Q.18** What are the requirements of the output stage of an OPAMP? Write the circuit of the output stage of the µA741 OPAMP. (7)

#### Ans:

#### **Requirements of the output stage of an OPAMP:**

- Should have low output impedance. Should be able to supply relatively large load currents without dissipating large amount of power.

- Should have a considerably large current gain so as to provide power amplification.

- Should be properly designed so as to have minimum parasitic capacitances.

#### Circuit for the output stage of OPAMP

- Output stage is class AB push-pull stage with  $Q_1 \& Q_2$  (Minimizing crossover distortion)

- $Q_3 \& Q_4$  provide means of short circuit protection when o/p is a ceidently connected to grand.

- $Q_5 \& Q_6$  help in biasing the transistors to work in class AB mode.

- Output impedance 75 r

- Output voltage swing-:  $Vo_{max} = V_{CC} V_{cesat} V_{BE} Vomin_{=} V_{EE+}V_{CESAT} + 2V_{EB}$

- Max output current (sinking or sourcing) = 20 MA

# www.StudentBounty.com Homework Help & Pastpaper

Circuit of output stage of OP amp

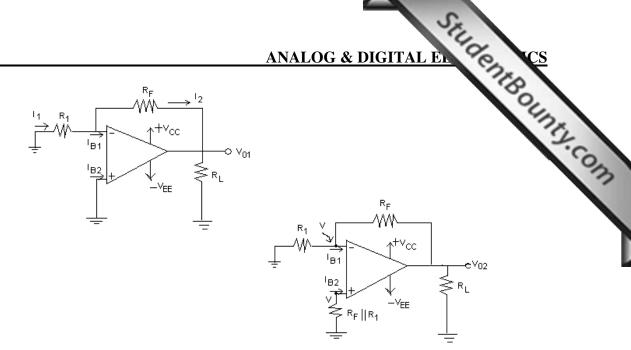

Q.19 Why do you require dc level shifting in OPAMPs? What are the requirements of the level shifting stage? Write a typical circuit for measuring the input bias current of an OPAMP and explain the procedure for measurement.(9)

#### Ans:

#### **DC level shifting in OPAMPS**

Because of the multiple gain stages used in an OPAMP, the DC level needs to be restored before signal can be fed into the next gain stage. Thus DC level shifting is required.

#### **Requirements for level shifting stage:-**

- Should bring the dc level of the signal down to zero without affecting the ac component of the signal.

- Should have high input impedance and low output impedance to the a.c. component as it behaves as an intermediate stage coupling two stages in an OPAMP.

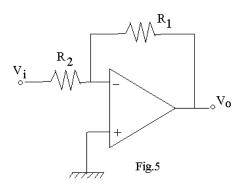

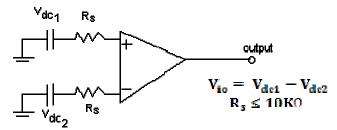

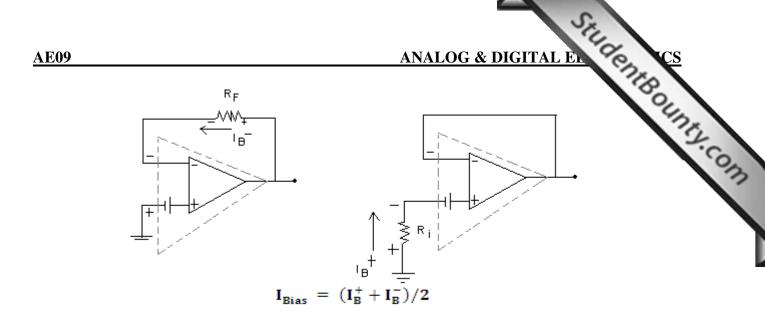

#### Circuits for measuring input bias current of an OPAMP are:

Assumptions

$\begin{aligned} \textbf{-} \mathbf{V}_{i0} &= \mathbf{0} \\ \mathbf{I}_{B1} &= \mathbf{I}_{B2} = \mathbf{I}_{B} \textbf{-} \mathbf{I}_{i0} \end{aligned}$

#### ANALOG & DIGITAL EX

# **Procedure:** Measure V<sub>01</sub> • $\frac{+Vo_1}{R_f} = I_{B1}$ $Vo_1 = I_{B1} R_F - (i)$ $I_{B1} = \frac{V_{O1}}{R_F}$

Measure V<sub>02</sub>

$$I_{B1} = \frac{V_{O_2} - V}{R_F} - \frac{V}{R_I} = \frac{V_{O2}}{R_F} - V\left(\frac{1}{R_I} + \frac{1}{R_F}\right)$$

From (i)

$$V\left(R_F \parallel R_I\right)^{-1} = \frac{V_{O2}}{R_F} - \frac{V_{O1}}{R_F}$$

$$V = \left(\frac{R_I * R_F}{R_F + R_I}\right) \left(\frac{V_{O2}}{R_F} - \frac{V_{O1}}{R_F}\right) - (ii)$$

$$V = -I_{B2} - (R_F R_I)/(R_F + R_I) - - (iii)$$

$$I_{B2} (R_F \parallel R_1) = \left(\frac{R_1 R_F}{R_1 + R_F}\right) \left(\frac{V_{o_1} - V_{o_2}}{R_F}\right)$$

$$I_{B2} = \frac{V_{o_1} - V_{o_2}}{R_F}$$

From (ii) and (iii)

www.StudentBounty.com Homework Help & Pastpapers

ANALOG & DIGITAL EN

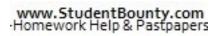

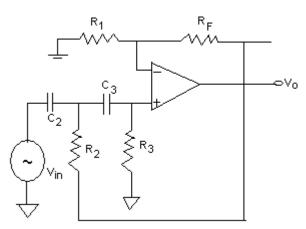

Q.20 What is an active filter? What is the role of the amplifier of the active filter? What limitations of active filters?

#### Ans:

#### **Active Filters**

StudentBounts.com A filter comprising of active elements such as OPAMPS, current conveyors etc along with passive elements so as to provide amplification along with filtering are called active filters.

## **Role of Amplifier is an active filter:**

- a) To provide a pass band gain.

- **b**) To provide buffering action to isolate the filter with the output stage.

- c) Improve the Q factor of the filter by using +ve feedback and improve tunability

- **d**) To realize universal filters

#### Limitations of active filters:

- Circuit more complex than conventional passive filters. Problems of instability and ringing.

- Dependence of filter parameters on device parameters which are difficult to control (like gain of OPAMP) and sensitive to temperature variations.

- Limited in usage up to medium frequencies. Difficult to realize an active filter at VHF owing to the limitation of OPAMPS.

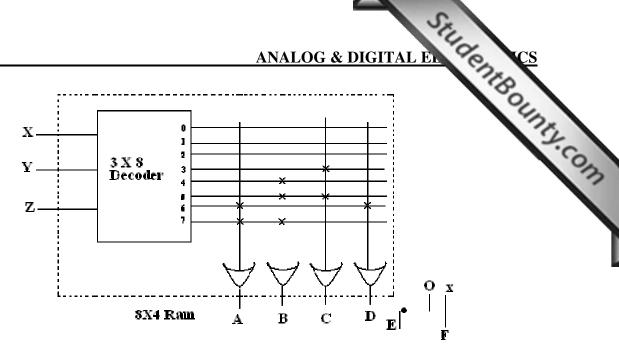

- Q.21 Design a combinational circuit that accepts a 3-bit number as input and generates an output binary number equal to the square of the input number using ROM. (9)

#### Ans:

The maximum no that can be at the o/p is (7)  $^2 = 49 = 110001$ Thus the output will be of 6 bit max

| X | У | Z | Α | B | С | D | E | F | Decimal |

|---|---|---|---|---|---|---|---|---|---------|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0       |

| 0 | 0 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1       |

| 0 | 1 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 4       |

| 0 | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 1 | 9       |

| 1 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 0 | 16      |

| 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 | 1 | 25      |

| 1 | 1 | 0 | 1 | 0 | 0 | 1 | 0 | 0 | 36      |

| 1 | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 49      |

From the truth table we can see that F is always equal Z and output E is always 0; so this is a constant. So we need to generate only 4 outputs with ROM. So minimum size of ROM needed must have 3 inputs and 4 outputs. Three inputs specify eight words so the ROM must be of size 8X4. x, y, z are three inputs and A, B, C and D are four outputs of the ROM.

ANALOG & DIGITAL EN

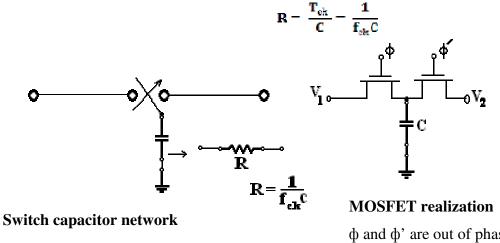

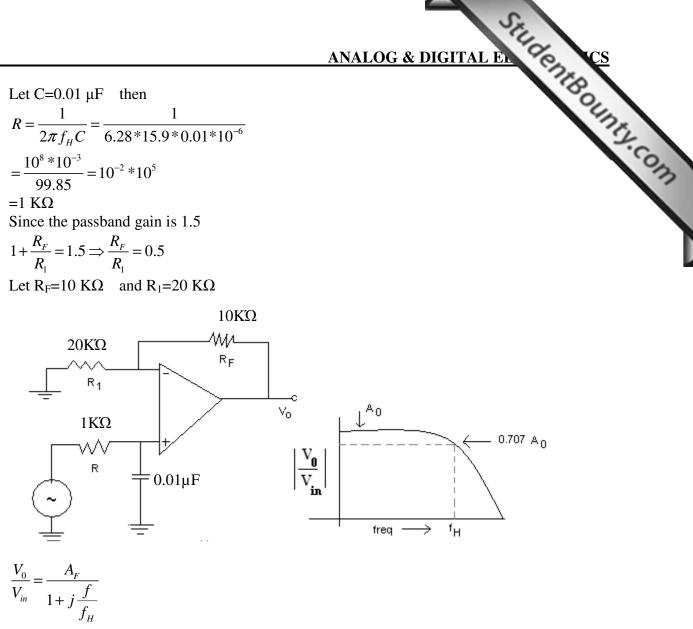

Q.22 What are the advantages of switched capacitor filters? Design a switched capacitor integrator for critical frequency of 20 Hz. Assume frequency of clock as 2 KHz. Compare with an RC integrator. (10)

#### Ans:

#### Advantages of Switched capacitor filters:

- No need of resistances which occupy a large space on chip and difficult to fabricate.

- Easy to simulate large value of resistances with available capacitances by changing the clock frequency.

- Easy to tune the circuit electronically as resistance and hence the filter parameters such as cut off frequency and Q-factor depend on the clock frequency.

- Suited for large scale integration of circuits for analog application.

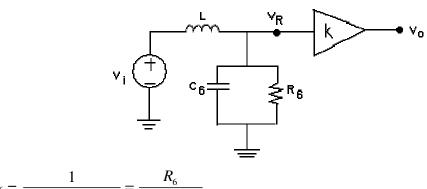

An RC integrator is given below and transfer function is given as

$f_0 = \frac{1}{2\pi R_1 C_f}$ ; unity gain frequency

The resistor R can be replaced by a switched capacitor  $C_1$  as shown below.

www.StudentBounty.com nework Help & Pastpapers

$\mathbf{R}_{1} = \frac{1}{\mathbf{C}_{1} \mathbf{f}_{ck}}$  where  $\mathbf{f}_{ck} = \text{clock frequency}$ Here

$\mathbf{2}$

**Design:** given  $f_0 = 20Hz$ ,  $f_{ck} = 2$  KHz.

ANALOG & DIGITAL EL

$$\frac{1}{c_{1}f_{ck}}$$

where  $f_{ck} = clock$  frequency

2 KHz.

$0 = \frac{C_{1}}{C_{F}} = \frac{f_{ck}}{2\pi} \Rightarrow \frac{C_{F}}{C_{1}} = 15.9$

So we choose  $C_F = 15.9 \text{ pF}$  and  $C_1 = 1 \text{ pF}$ .

For RC integrator if we take  $R_1 = 10 \text{ K}\Omega$  then C=0.79µF. This is a large value of capacitance. If we choose small value of capacitance let us say 10nF then  $R_1=0.795M\Omega$ . Fabrication of high value of R and C is not practical for a monolithic circuit, so switched capacitance is a better choice.

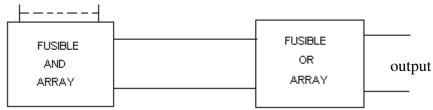

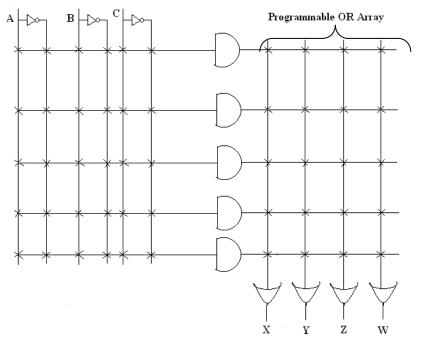

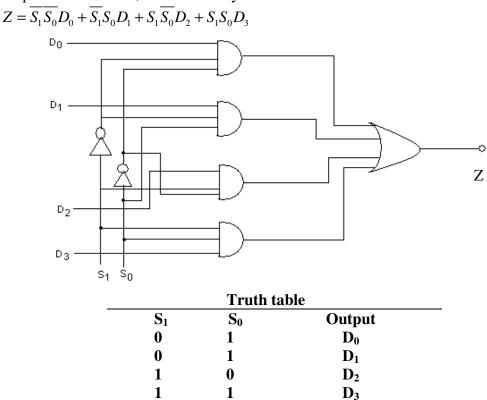

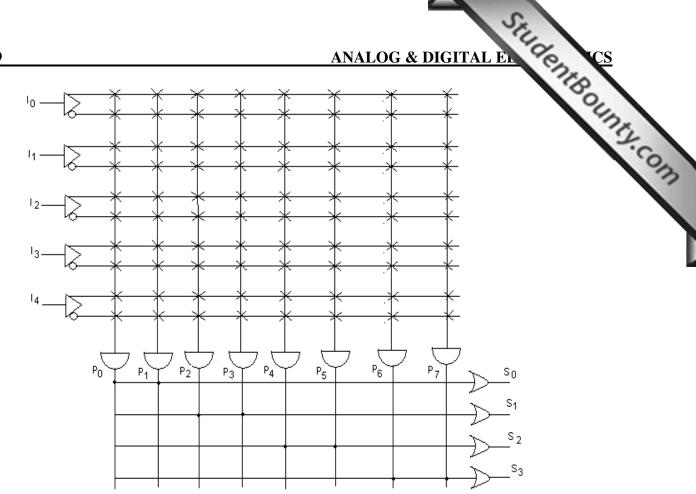

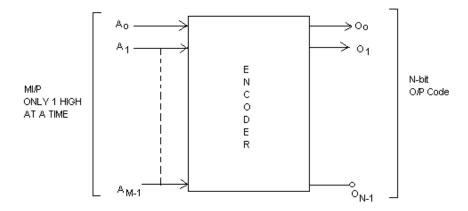

**Q.23** Write the general structure of a PLA. Write the logic diagram of a general  $n \times p \times m$  PLA. How are PLAs characterised? (6)

#### **Ans: Input**

#### **General structure of PLA**

PLAs along with PAL & ROM are included in the more general classification of IC's called Programmable Logic Devices (PLDs).

In each case input signals are presented to an array of AND gates while the outputs are taken from an array of OR gates. The PLA is much more versatile than PROM & PAL since both its AND gate array & OR gate array are fusible linked and programmable.

www.StudentBounty.com Homework Help & Pastpape

(6)

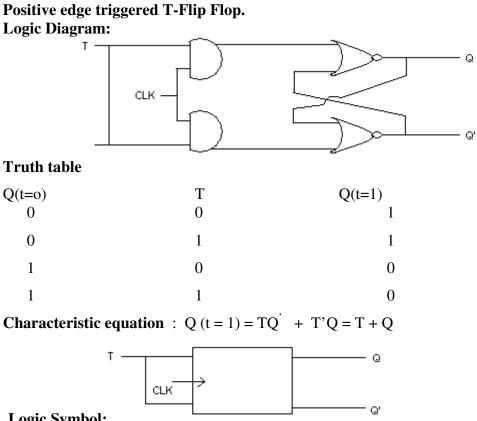

StudentBounts.com Write the logic diagram, truth table, and the logic symbol of a positive-edge-trig Q.24 flip-flop.

## Ans:

## Logic Symbol:

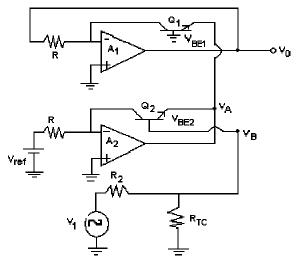

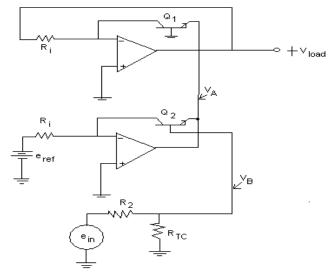

Q.25 Briefly explain the operation of an antilog amplifier circuit that uses two OPAMPS.

#### Ans: Antilog amplifier

From the figure above

**AE09**

www.StudentBounty.com nework Help & Pas

# ANALOG & DIGITAL EL CORPUSACION

$$V_{Q1BE} = \frac{KT}{q} \ln \frac{V_{load}}{R_i I_s}$$

$$V_{Q2BE} = \frac{KT}{q} \ln \frac{e_{ref}}{R_i I_s}$$

KT

Since the base of Q1 is tied to ground  $V_A = -V_{O1BE}$ , therefore

$$V_A = -\frac{KT}{q} \ln \frac{V_{load}}{R_i I_s}$$

$V_B$  is the base voltage of  $Q_2$  and is output from the  $R_2$ ,  $R_{TC}$  voltage divider.

$$V_B = V_{Q2Base} = \frac{R_{TC}}{R_2 + R_{TC}} e_{in}$$

The voltage at the emitter of  $Q_2$  is

$$V_{Q2E} = V_{Q2base} + V_{Q2BE}$$

On substitution, we get

$$V_{Q2E} = \frac{R_{TC}}{R_2 + R_{TC}} e_{in} - \frac{KT}{q} \ln \frac{e_{ref}}{R_i I_s}$$

But the emitter of  $Q_2$  is  $V_A$  thus

$$V_{A} = -\frac{KT}{q} \ln \frac{V_{load}}{R_{i}I_{s}} = \frac{R_{TC}}{R_{2} + R_{TC}} e_{in} - \frac{KT}{q} \ln \frac{e_{ref}}{R_{i}I_{s}}$$

$$\frac{R_{TC}}{R_{2} + R_{TC}} e_{in} = -\frac{KT}{q} \left( \ln \frac{V_{load}}{R_{i}I_{s}} - \ln \frac{e_{ref}}{R_{i}I_{s}} \right)$$

$$-\frac{q}{KT} \frac{R_{TC}}{R_{2} + R_{TC}} e_{in} = \ln \frac{V_{load}}{e_{ref}}$$

$$\frac{V_{load}}{e_{ref}} = 10^{-Ke_{in}}$$

$$therefore$$

$$V_{load} = e_{ref} 10^{-Ke_{in}}$$

$$Where \ K = 0.4343 \frac{q}{KT} \frac{R_{TC}}{R_{2} + R_{TC}}$$

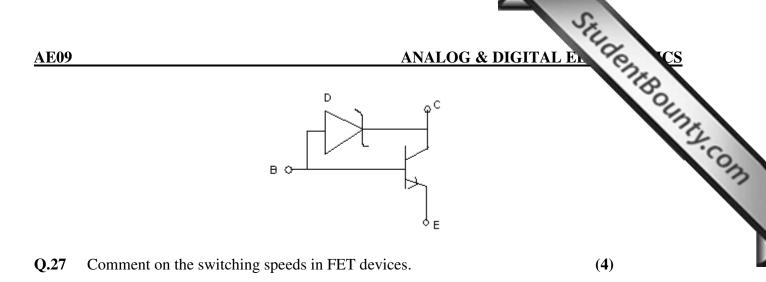

Q.26 Briefly explain how the speed of a transistor response can be improved by preventing the transistor from going into saturation. (4)

#### Ans:

The storage delay time can be reduced considerably by preventing the transistor from going into saturation. One way of achieving this is to connect a Schottky diode between the base and collector of the transistor. When the transistor is in the active region, the diode D is reverse based. The diode conducts when the base-collector junction voltage falls to about 0.4v and does not allow the collector junction voltage to fall lower than 0.4V below the base voltage. Hence the collector junction is not sufficiently forward-biased and the transistor is thus prevented from entering into Saturation.

#### www.StudentBounty.com nework Help & Pastpa

### Ans:

### Comment on the switching speeds in FET devices:

FET devices are slower in terms of operating speed and are susceptible to static charge damage. For MOS logic,  $t_{pd}$  =50 ns. The propagation delay associated with MOS gate is large (50ns) because of their high output resistance ( $\approx 100 k\Omega$ ) and capacitive loading present at the driven gates.

Thus, if we apply a square pulse at the gate of an FET, the gate voltage takes some time to rise due to the input capacitance & thus switching becomes slower.

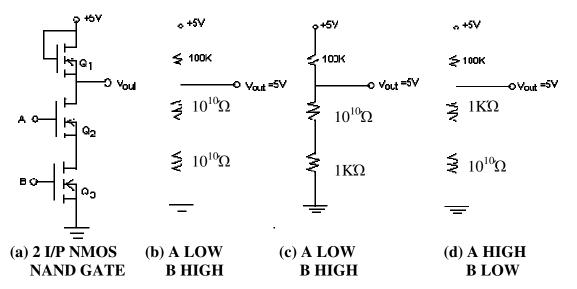

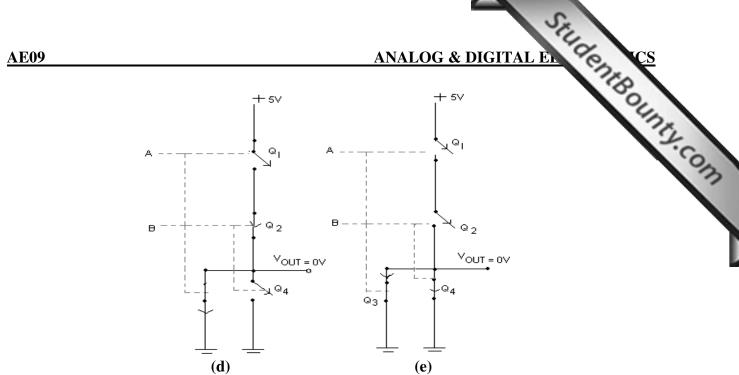

Q.28 What are the advantages of CMOS gates? Briefly explain an NMOS two-input NAND gate. Assume that positive logic is intended. What is 'SOS' as used in IC technology?(8)

### Ans:

The CMOS logic family uses both P and N channel MOSFETs in the same circuit to realize several advantages over PMOS and NMOS families. The CMOS family is faster and consumes less power than other MOS families. CMOS devices can be operated at higher voltage resulting in increased noise immunity.

NMOS and input NAND gate

The following fig shows two input NMOS NAND gate & its equivalent circuit for different possible combinations of inputs in terms of resistance values of transistors in ON and OFF positions.

www.StudentBounty.com Homework Help & Pastpapers

### ANALOG & DIGITAL EN

'SOS' is a relatively new IC fabrication technology named as "silicon-on-Saph

StudentBounty.com Q.29 What is TTL? Illustrate the simplest and most elemental form of a TTL gate by a ske and explain its operation when the input to the gate is 'HIGH' and 'LOW'. What is the main reason for the speed limitation of TTL? How can this be eliminated?

### Ans:

TTL stands for "Transistor – Transistor Logic" It is the most popular logic family and also the most widely used bipolar digital IC family. It uses transistors operating in saturated mode. Good speed, low manufacturing cost, wide range of circuits and availability in SSI & MSI are its merits.

### **Open collector TTL inverter.**

When the input is high, the diode D is reverse biased & thus OFF. Moreover, transistor  $Q_1$  is in cut off mode. Thus, the current through  $R_1$  suffers a small voltage drop across the base – collector junction of  $Q_1$  and hence switches on  $Q_2$ . The emitter current of  $Q_2$  (which will be  $(\beta+1)$  times the base current) switches transistor Q<sub>3</sub> ON. Since the emitter of Q<sub>3</sub> is grounded, the collector is also at near ground potential, thus low. But when the input is low, the diode D is F/B and  $Q_1$  is ON. The enough base drive is not available for  $Q_2$  to turn ON. As a result  $Q_3$ is also OFF. Due to this, the collector of Q<sub>3</sub> is floating. To prevent this, we have a passive pull up resistor, which takes the O/P to +5V in case Q<sub>3</sub> is off.

### **Open collector TTL inverter**

The open collector arrangement is much slower than the totem pole arrangement, because the time constant with which the load capacitance charges in this case is considerably larger. (In the case of totem pole output, it is active pull up. Thus the output rises fast). For this reason, the open collector circuits should not be used in applications where switching speed is a principal consideration.

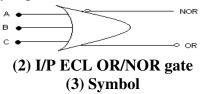

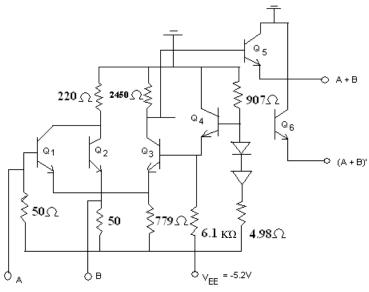

**Q.30** In what type of applications is the ECL recommended? Justify its suitability in such application. Write the circuit of a 3-input ECL OR/NOR gate and mention its features. What is its logic symbol? (8)

### Ans:

ECL is recommended in high frequency applications where its speed is superior.

### Justification:

a. It is not saturated logic, in the sense that transistors are not allowed to go into saturation. So, storage time delays are eliminated & therefore the speed of operation is increased.

### **ANALOG & DIGITAL EX**

- b. Currents are kept high, and the output impedance is so low that circul capacitances can be quickly charged and discharged.

- c. The limited voltage swing that is the logic levels are chosen clock to each other.

**Circuit of ECL OR/NOR Gate**

### **Important features:**

- 1) One advantage of differential input circuit in ECL gates is that it provides common mode rejection - power supply noise common to both sides of the differential configuration is effectively cancelled out.

- 2) Also, since the ECL output is produced at an emitter follower, the output impedance is desirably low. As a consequence, the ECL gates not only have a larger fan out but also are relatively unaffected by capacitive loads.

Two binary numbers  $A_2A_1A_0$  and  $B_2B_1B_0$  ( $A_0 \& B_0 : LSB's$ ) are to be added. Draw Q.31 the scheme of a parallel binary adder consisting of half adders and explain its operation. (7)

Ans:

H<sub>A</sub> Cascaded with another forms of F<sub>A</sub> (Full Adder)

### **AE09**

### <u>ANALOG</u> & DIGITAL EX

### **Operation:**

StudentBounty.com The first  $FA_0$  adding the LSB,  $A_0$  and  $B_0$  is essentially a half adder whose sum bit is and Cout since Cin is set to 0. The Cout of the addition of LSB's is carried over to the add of next bits i.e.A<sub>1</sub>,B<sub>1</sub> which are added using a full adder, FA<sub>1</sub> This procedure continues all the next adders being full adders till the MSB's, A<sub>3</sub> & B<sub>3</sub>. The final sum is  $S_4S_3S_2S_1S_0$  Where  $S_4$  is the MSB and so is the LSB.