Code: AE54/AC54/AT54

Subject: LINEAR ICs & DIGITAL ELE

**ROLL NO.**

## AMIETE - ET/CS/IT

**Time: 3 Hours**

## **DECEMBER 2013**

StudentBounty.com PLEASE WRITE YOUR ROLL NO. AT THE SPACE PROVIDED ON EACH PAGE IMMEDIATELY AFTER RECEIVING THE QUESTION PAPER.

### **NOTE: There are 9 Questions in all.**

- Ouestion 1 is compulsory and carries 20 marks. Answer to Q. 1 must be written in the space provided for it in the answer book supplied and nowhere else.

- The answer sheet for the Q.1 will be collected by the invigilator after 45 minutes of the commencement of the examination.

- Out of the remaining EIGHT Questions answer any FIVE Questions, selecting at least TWO questions from each part, each question carries 16 marks.

- Any required data not explicitly given, may be suitably assumed and stated.

#### **Q.1** Choose the correct or the best alternative in the following: $(2 \times 10)$

a. Karnaugh Map uses \_\_\_\_\_

(A) Binary Code (C) BDC Code

(B) Grev Code (D) Both (A) and (B)

b. For impedance matching application, OP-AMP is used as a \_\_\_\_\_

(A) Voltage Follower (C) Voltage Clipper

(B) Voltage Clamper (D) Voltage Multiplier

c. An Integrated Circuit which consists of  $10^6 - 10^7$  transistors / chip is called as

- (A) Medium Scale Integration (C) Very Large Scale Integration

- (B) Large Scale Integration

(D) Ultra Large Scale Integration

d. The output voltage  $(V_0)$  for the OP-AMP circuit of Fig.1 is \_\_\_\_\_ V<sub>0</sub> (A)  $Vo = V_3 - (V_1 + V_2)$ **(B)**  $Vo = V_3 + (V_1 + V_2)$ (C)  $Vo = -V_3 + (V_1 + V_2)$ **(D)**  $Vo = -V_3 - (V_1 + V_2)$ R

AE54/AC54/AT54 / DECEMBER - 2013

1

AMIETE - ET/CS/IT

#### Code: AE54/AC54/AT54 Subject: LINEAR ICs & DIGITAL ELE

studentBounty.com e. For which of the following flip-flops, the output is clearly defined for the combinations of two inputs \_\_\_\_\_

(A) D type flip-flop (C) J-K flip-flop

(**B**) R-S flip-flop (D) None of these **ROLL NO.**

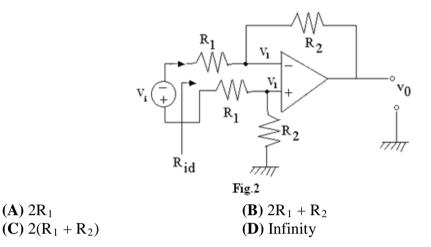

f. For the circuit of Fig.2, the input resistance R<sub>id</sub> will be \_\_\_\_\_

g. The number of states in its counting sequence that a Ring Counter consisting of 'n' flip-flops is \_\_\_\_

| $(A) + 2^{n-1}$ | <b>(B)</b> $2^{n+1}$ |

|-----------------|----------------------|

| ( <b>C</b> ) n  | ( <b>D</b> ) n-1     |

h. A one-to-sixteen demultiplexer requires

| (A) 2 select input lines | <b>(B)</b> 3 select input lines |

|--------------------------|---------------------------------|

| (C) 8 select input lines | <b>(D)</b> 4 select input lines |

- i. The A/D converter which has maximum speed of conversion is \_\_\_\_\_

- (A) Successive-approximation A/D converter (B) Parallel-comparative A/D converter (C) Counter ramp A/D converter

- (D) Dual-slope A/D converter

- j. Boolean Algebra states that the "OR ing of several variables results in the same regardless of the grouping of the variables" is called \_\_\_\_\_

- (A) Commutative Property (C) Distributive Property

(B) Associative Property (**D**) All of these

PART (A) Answer At least TWO questions. Each question carries 16 marks.

AE54/AC54/AT54 / DECEMBER - 2013

2

AMIETE - ET/CS/IT

# Code: AE54/AC54/AT54 Subject: LINEAR ICs & DIGITAL ELE

| de: A | E5 | 4/AC54/AT54 Subject: LINEAR ICs & DIGITAL ELE                                                                                                                                                                                                           | 210                 |

|-------|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| Q.2   | a. | Enlist the various advantages of IC over discrete component circuits.                                                                                                                                                                                   | an ()               |

|       | b. | Draw basic differential amplifier and discuss transfer characteristics of a ideal operational amplifier.                                                                                                                                                | an<br>(8)           |

|       | c. | Design an amplifier with a gain of +5 using one OP-AMP                                                                                                                                                                                                  | (4)                 |

| Q.3   | a. | State non-ideal DC characteristics of an op-amp. Explain any two of the in detail.                                                                                                                                                                      | em (8)              |

|       | b. | <ul> <li>(i) Define Slew Rate of an op-amp</li> <li>(ii) What causes the Slew Rate</li> <li>(iii) How Slew Rate is measured</li> <li>(iv) Can IC 741C be used for high frequency application?</li> </ul>                                                | (4×2)               |

| Q.4   | a. | Draw the characteristics of an ideal comparator and that of a commercial available comparator. Also list different types of comparators.                                                                                                                | ully (6)            |

|       | b. | Explain the following in detail using OP-AMP, assuming 1-V peak square wave as input signal for<br>(i) Positive clipper (ii) Negative Clamper                                                                                                           | to peak<br>(2×4)    |

|       | c. | State the applications of a precision diode.                                                                                                                                                                                                            | (2)                 |

| Q.5   | a. | Describe the operation of an Astable multivibrator using 555 timer.                                                                                                                                                                                     | (8)                 |

|       | b. | Calculate the values of LSB, MSB and full scale output for an 8-bit D the 0 to 10V range.                                                                                                                                                               | AC for (6)          |

|       | c. | What is a voltage regulator? State only name of the circuits that are make a regulated power supply.                                                                                                                                                    | used to (2)         |

|       |    | PART (B)<br>Answer At least TWO questions. Each question carries 16 marks.                                                                                                                                                                              |                     |

| Q.6   | a. | Differentiate between positive logic and negative logic.                                                                                                                                                                                                | (4)                 |

|       | b. | Perform the following conversions:<br>(i) $(110011011001)_2 = (\_\_\_]_{10}$ (ii) $(268)_{10} = (\_\_]_{16}$<br>(iii) $(39.12)_{10} = (\_\_]_2$ (iv) $(1054)_8 = (\_\_]_{10}$<br>(v) $(2040.125)_{10} = (\_\_]_{16}$ (vi) $(1001101.1011)_2 = (\_\_]_8$ | (6×2)               |

| Q.7   | a. | Why NAND and NOR gates are called universal gates?                                                                                                                                                                                                      | (6)                 |

|       | b. | Prove that the given identity $Y = \overline{A + B}$ represents a NOR logic.                                                                                                                                                                            | (4)                 |

|       | c. | (i) Draw the logic circuit for the given identity $Y = ABC + \overline{ABC} + B$<br>(ii) Simplify the expression and draw a logic circuit for the same.                                                                                                 | (2×3)               |

| Q.8   | a. | What is Priority encoder? Draw & explain the truth table of decimal to priority encoder.                                                                                                                                                                | BCD<br>( <b>8</b> ) |

|       |    |                                                                                                                                                                                                                                                         |                     |

AE54/AC54/AT54 / DECEMBER - 2013

AMIETE - ET/CS/IT

om

3

Subject: LINEAR ICs & DIGITAL ELE Code: AE54/AC54/AT54

studentBounty.com b. Design a Full Adder Circuit consisting of three inputs A, B, C<sub>IN</sub> and two outputs S, C<sub>OUT</sub>.

**ROLL NO.**

- Q.9 a. Write short notes on:-(i) NAND gate latch (ii) Clocked D FF  $(2\times4)$

- b. If data 1101 is fed into 4 bit Serial In / Serial Out Shift Register, show the status of register at various clock pulses. (6)

- c. State one advantage and one disadvantage of synchronous counter over asynchronous counter. (2)