**Subject: VLSI DESIGN**

**JUNE 2011**

NOTE: There are 9 Questions in all.

Time: 3 Hours

- Student Bounty Com Question 1 is compulsory and carries 20 marks. Answer to Q.1 must be written in the space provided for it in the answer book supplied and nowhere else.

- The answer sheet for the Q.1 will be collected by the invigilator after 45 Minutes of the commencement of the examination.

- Out of the remaining EIGHT Questions answer any FIVE Questions. Each question carries 16 marks.

- Any required data not explicitly given, may be suitably assumed and stated.

| 0.1 | Choose the correct or t | he hest altern | sative in the following: |  |

|-----|-------------------------|----------------|--------------------------|--|

$(2\times10)$

Max. Marks: 100

- a. Substrate in nMOS FET is

- (A) N type

(B) P type

(C) PN type

- (D) None

- b. In depletion mode FET devices channel is established when

- (A)  $V_{gs} = V_{DD}$

**(B)**  $V_{gs} > V_t$

(C)  $V_{gs} = 0$

(**D**)  $V_{gs} > V_{DD}$

- c. Transit time  $\tau_{sd}$  is

- (A)  $\frac{\text{Valocity}}{\text{Channel length}}$

$\frac{Channel\ length}{Velocity}$

Charge Electric field

- **(D)**  $\frac{\text{Channel length}}{\text{Electric field}}$

- $\frac{Z_{pu}}{}$  for nMOS inverter driven by another nMOS d. Pull-up to Pull-down ratio

inverter is

(A) 8:1

**(B)** 4:1

**(C)** 6:1

- **(D)** 16:1

- e. Implant in depletion type transistor is indicated by dotted square of dimension

- (A)  $6\lambda \times 6\lambda$

**(B)**  $8\lambda \times 8\lambda$

(C)  $4\lambda \times 4\lambda$

- **(D)**  $16\lambda \times 16\lambda$

- f. Total channel resistance of nMOS inverter when it is ON is

- (A)  $20 k \Omega$

**(B)**  $30 \text{ k}\Omega$

(C)  $40 \text{ k}\Omega$

(**D**)  $50 \text{ k} \Omega$

|     |                                                             |                                                                                                                      |                                                         | E.                   |

|-----|-------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------------|

|     | g.                                                          | Static power dissipation is low in _                                                                                 | inverter.                                               | Tall                 |

|     |                                                             | (A) PMOS<br>(C) CMOS                                                                                                 | (B) nMOS<br>(D) nMOS & CMOS                             | CHILDENH BOUNTS! COM |

|     | h.                                                          | Scaling factor for Gate Area is                                                                                      |                                                         | 7.60                 |

|     |                                                             | (A) $1/\beta^2$ (C) $1/\beta$                                                                                        | ( <b>B</b> ) $1/\alpha^2$ ( <b>D</b> ) $1/\alpha$       | 133                  |

|     | i                                                           | In nMOS pass Transistor                                                                                              | (2) 17 68                                               | •                    |

|     | 1.                                                          | -                                                                                                                    | -                                                       |                      |

|     |                                                             | (A) Tristate<br>(C) Low                                                                                              | ( <b>B</b> ) High and low ( <b>D</b> ) High             |                      |

|     | j.                                                          | D-algorithm is used to test                                                                                          | circuit                                                 |                      |

|     |                                                             | <ul><li>(A) Combinational</li><li>(C) Both (A) and (B)</li></ul>                                                     | <ul><li>(B) Sequential</li><li>(D) Flip-Flops</li></ul> |                      |

|     |                                                             | Answer any FIVE Question<br>Each question ca                                                                         | _                                                       |                      |

| Q.2 | a.                                                          | a. Write the cross-sectional view of nMOS enhancement and deplet Transistor indicating all the layers and terminals. |                                                         | de <b>(6)</b>        |

|     | b. With neat sketch explain the P-Well Fabrication process. |                                                                                                                      | ell Fabrication process.                                | (10)                 |

| Q.3 | a.                                                          | a. Derive the expression for $I_{ds}$ starting from transit time.                                                    |                                                         | (8)                  |

| b.  |                                                             | What are the different types of pull-ups are used in MOS circuit? Explain briefly with neat sketch.                  |                                                         | n<br>(8)             |

| Q.4 | a.                                                          | Draw & explain the circuit dia $\bar{f} = x + yz$                                                                    | gram and stick diagram for logic                        | function (8)         |

|     | b.                                                          | With neat diagram explain design                                                                                     | rules for wires and contact?                            | (8)                  |

| Q.5 | a.                                                          | Define sheet resistance and standar                                                                                  | rd unit of capacitance.                                 | (4)                  |

|     | b.                                                          | Derive the expression for total delarge capacitive load                                                              | elay when N inverters are cascaded                      | to drive (6)         |

**(6)**

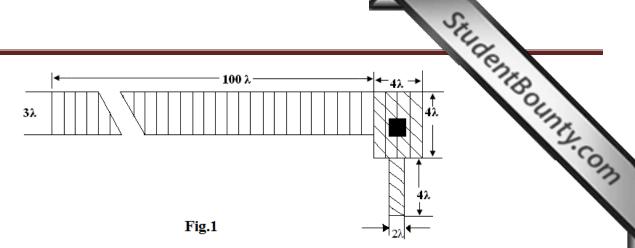

c. Calculate the total capacitance for the Fig.1.

- **Q.6** a. Derive the scaling factors for

- (i) Gate capacitance

- (ii) Operating frequency

- (iii) Power dissipation

**(8)**

- b. Explain how transmission gate eliminates degradation of output levels.

Write the circuit of 4:1 MUX using Transmission gate.

- Q.7 a. Explain design methodology steps to design complex VLSI circuit. (6)

- b. Design a 4 bit adder and obtain the expression for Sum, Carry & Half Sum.(10)

- Q.8 a. Draw and explain the circuit and stick diagram of nMOS-pseudo static memory cell. (8)

- b. Discuss the methods for optimisation of area, power dissipation and time of CMOS inverter.

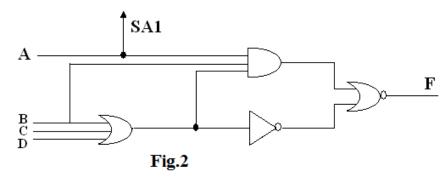

- Q.9 a. Explain the method for detection of stuck at faults using sensitized path based testing technique. Determine the test vector for SA1 detection for the circuit shown in Fig.2.

b. Draw the circuit of BILBO and explain briefly.