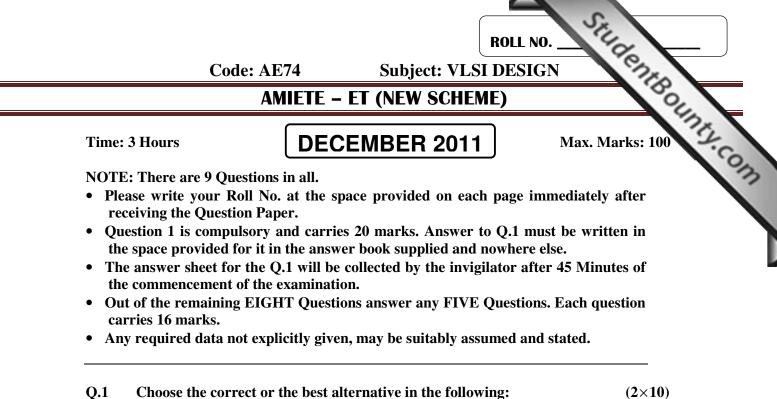

## Zer Chouse the correct of the best alternative in the following:

a. Which of the following layer developed first during fabrication?

| (A) Source | ( <b>B</b> ) Drain         |

|------------|----------------------------|

| (C) Gate   | ( <b>D</b> ) Metal Contact |

b. The Gate capacitance of a MOS Transistor is given by

| (A) $\frac{\epsilon_{\text{ins}}\epsilon_0 \mu}{D}$           | $(\mathbf{B}) \; \frac{\in_{\mathrm{ins}} \in_{\mathrm{O}} \mathrm{A}}{\mathrm{V}_{\mathrm{gs}}}$ |

|---------------------------------------------------------------|---------------------------------------------------------------------------------------------------|

| (C) $\frac{\epsilon_{\text{ins}}\epsilon_0 A}{I_{\text{ds}}}$ | $(\mathbf{D}) \stackrel{\in_{\mathrm{ins}}\in_{\mathrm{O}} \mathrm{WL}}{\mathrm{D}}$              |

c. The Trans-conductance of a MOS device can be increased by increasing its

| (A) Length | (B) Threshold Voltage      |

|------------|----------------------------|

| (C) Width  | <b>(D)</b> Oxide thickness |

d. Two NMOS pass transistors with  $V_t = 1.2V$  are connected in cascade such that drain of first is connected to source of the next and gate of both MOS are connected to 5V. The Output voltage  $V_o$  is

| (A) 2.6V          | <b>(B)</b> 3.8V |

|-------------------|-----------------|

| ( <b>C</b> ) 1.2V | ( <b>D</b> ) 0V |

e. The sheet resistance of a square is \_\_\_\_\_\_ to its thickness.

| (A) inversely proportional | ( <b>B</b> ) directly proportional |

|----------------------------|------------------------------------|

| (C) not related            | ( <b>D</b> ) equal                 |

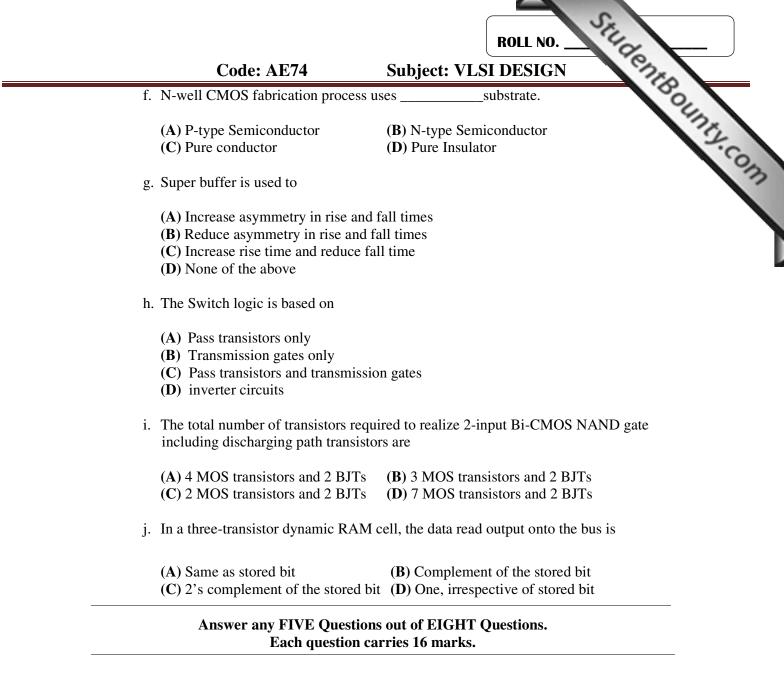

AE74 / DEC \_ 2011

1

- Q.2 a. Explain the action of N-MOS Enhancement mode transistor for different values of  $V_{gs}$  and  $V_{ds}$ . (8)

- b. What are the advantages of E-beam masks? Differentiate between Raster scanning and Vector scanning. (4)

- c. Draw the cross-sectional view of p-well CMOS inverter and indicate the input, output and supply voltages. (4)

Q.3 a. Calculate the threshold voltage with  $\epsilon_{si}$ =11.7,  $\epsilon_{ox}$ =3.9 for an N-MOS transistor

with

$$N_A = 2 \times 10^{17} / \text{cm}^3$$

,  $t_{ox} = 190 \text{ Å}^\circ$ . Assume  $\Phi_{ms} = -0.85 \text{V}$ ,  $N_i = 1.45 \times 10^{10} / \text{cm}^3$

and  $Q_{fc} = Q_{ss} = V_{SB} = 0$ . (8)

b. Explain the CMOS inverter transfer characteristics by highlighting the regions of operation of the MOS transistor. (8)

AE74 / DEC \_ 2011

2

|     |    | Code: AE74 Subject: VLSI DESIGN                                                                                                                                                                                         | 1974            |

|-----|----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| Q.4 | a. | Discuss $\lambda$ -based n-MOS design rules for wires and contacts.                                                                                                                                                     | (8) 60          |

|     | b. | Describe the monochrome stick encoding of:                                                                                                                                                                              | 32              |

|     |    | <ul><li>(i) Simple n-well based BiCMOS inverter</li><li>(ii) 2-input CMOS NAND gate.</li></ul>                                                                                                                          | (8)             |

| Q.5 | a. | Derive the expressions for rise time and fall time of CMOS inverter and                                                                                                                                                 |                 |

|     |    | that $\tau_r = 2.5 \tau_f$ for equal n and p-transistor geometries.                                                                                                                                                     | (8)             |

|     | b. | Find the static on-state resistance of a 4:1 N-MOS inverter and minimum s CMOS inverter. (Assume on resistance of minimum sized NMOS enhance transistor as $10K\Omega$ )                                                |                 |

|     | c. | Draw the circuit of non inverting type N-MOS super buffer.                                                                                                                                                              | (2)             |

| Q.6 | a. | <ul> <li>Obtain the Scaling Factors for the following Device Parameters:</li> <li>(i) Switching energy per gate</li> <li>(ii) current density</li> <li>(iii) gate delay</li> <li>(iv) gate capacitance</li> </ul>       | (8)             |

|     | b. | Realize 4:1 multiplexer using N-MOS switches.                                                                                                                                                                           | (4)             |

|     | c. | Show that for an 8:1 N-MOS inverter with minimum sized pull-down tran the on state power dissipation is $0.28 \text{ mw}$ . (Power supply = 5V)                                                                         | usistor,<br>(4) |

| Q.7 | a. | Discuss the linking of the subunits using one bus, two bus and three architectures with suitable diagrams.                                                                                                              | ee bus<br>(8)   |

|     | b. | Design a single bit adder and implement 4-bit ALU functions using elements.                                                                                                                                             | adder<br>(8)    |

| Q.8 | a. | What are the system timing considerations?                                                                                                                                                                              | (6)             |

|     | b. | Explain with circuit diagram the functioning of a three-transistor dynamic RAM cell. What are the conditions for no power dissipation in the cell?                                                                      | (6)             |

|     | c. | What are noise margins? Write the CMOS inverter noise margin equations the help of CMOS inverter transfer characteristics.                                                                                              | with (4)        |

| Q.9 |    | Write short notes on (Any <u>FOUR</u> ): (4                                                                                                                                                                             | ×4)             |

|     |    | <ul> <li>(i) CAD tools for VLSI design</li> <li>(ii) Design for testability</li> <li>(iii) Testing sequential logic</li> <li>(iv) Built-In-Self-Test (BIST)</li> <li>(v) Ground rules for successful design.</li> </ul> |                 |