| Candidate | Centre | Candidate |  |

|-----------|--------|-----------|--|

| Name      | Number | Number    |  |

|           |        | 0         |  |

# **GCSE**

294/02

ELECTRONICS

MODULE TEST E2

HIGHER TIER

P.M. FRIDAY, 6 June 2008 45 minutes

For Examiner's use only

#### ADDITIONAL MATERIALS

In addition to this examination paper you may need a calculator.

### INSTRUCTIONS TO CANDIDATES

Write your name, centre number and candidate number in the spaces at the top of this page. Answer **all** the questions in the spaces provided in this booklet.

### INFORMATION FOR CANDIDATES

The number of marks is given in brackets at the end of each question or part-question.

## Answer all questions

1. The diagram shows the arrangement of the LEDs in a seven-segment display.

Complete the following table.

| Segments |   |   |   |   | Number |   |           |  |

|----------|---|---|---|---|--------|---|-----------|--|

| a        | b | с | d | e | f      | g | Displayed |  |

| 1        | 1 | 1 |   |   |        |   | 7         |  |

| 1        | 1 | 1 | 1 | 0 | 0      | 1 |           |  |

[2]

**2.** (a) Complete the truth tables for the following logic gates:

(i) a **NOT** gate [1]

| Input | Output |

|-------|--------|

| 0     |        |

| 1     |        |

(ii) an AND gate

[1]

| Inp | Output |  |

|-----|--------|--|

| 0   | 0      |  |

| 0   | 1      |  |

| 1   | 0      |  |

| 1   | 1      |  |

[2]

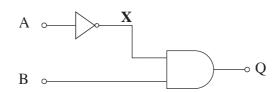

(b) Complete the following truth table for this system.

| Input A | Input B | X | Q |

|---------|---------|---|---|

| 0       | 0       |   |   |

| 0       | 1       |   |   |

| 1       | 0       |   |   |

| 1       | 1       |   |   |

(c) (i) Complete the diagram to show how a NAND gate can be made to behave as a NOT gate. [1]

(ii) Draw a diagram to show the NAND gate equivalent of an AND gate [1]

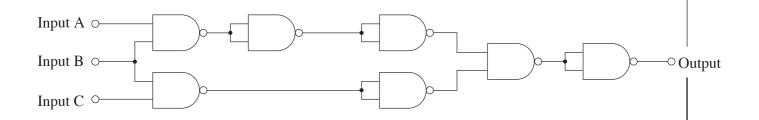

(iii) Here is a logic system built using only NAND gates.

Cross out all redundant gates

[1]

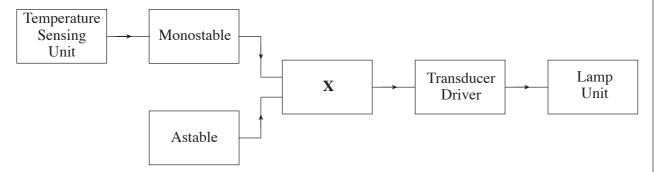

3. Here is the block diagram for a freezer alarm.

The lamp does not light when the freezer is cold enough.

The lamp flashes on and off repeatedly when the freezer is too hot.

The monostable outputs a logic 1 signal for 30 s when the freezer gets too hot.

(a) What type of logic gate is required in block **X**?

[1]

Answer .....

(b) What is the job of the astable in this system?

Choose one of the following answers:

- A. It makes the Lamp Unit pulse on and off over and over again.

- **B.** It outputs a steady logic 1 signal when the freezer gets too hot.

- **C.** It keeps the Lamp Unit switched on for 30s and then switches it off automatically.

- **D.** It buffers the output of the monostable, providing enough current to light the lamp.

[1]

Answer .....

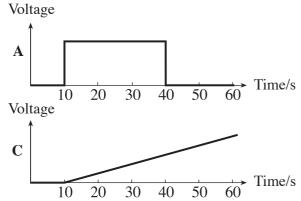

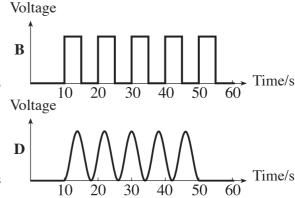

(c) The temperature in the freezer rises and triggers the monostable.

Which of the following shows the output signal from the monostable?

[1]

[2]

Answer .....

(d) The monostable time delay can be found from the formula

**T = 1.1 RC** (where T is in seconds, R is in MΩ and C is in  $\mu$ F)

This can be re-arranged into the form:

$$\mathbf{R} = \frac{\mathbf{T}}{1.1\mathbf{C}}$$

The monostable circuit uses a 470 µF capacitor.

Calculate the value of resistance needed to produce a time delay of 30 s.

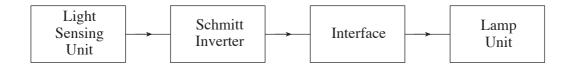

**4.** The block diagram shows the design of a security light, which turns on automatically when it gets dark.

- (a) The Light Sensing Unit gives out a logic 0 signal in the dark.

- (i) The Schmitt Inverter inverts the signal from the Light Sensing Unit.

|      | Explain what this sentence means.                             | [1] |

|------|---------------------------------------------------------------|-----|

|      |                                                               |     |

| (ii) | What is the other use of the Schmitt Inverter in this system? | [1] |

|      |                                                               |     |

(b) Here is part of a data sheet for a Schmitt Inverter:

When connected to 5 V supply:

- Logic 0 = 0 V

- Logic 1 = 5 V

- The output changes from logic 1 to logic 0 when a **rising** input voltage reaches 3 V

- The output changes from logic 0 to logic 1 when a **falling** input voltage reaches 1 V

The input signal for the Schmitt Inverter is shown below.

Use the axes provided to draw the resulting output signal produced by the Schmitt Inverter.

Time

0

| (i)         | Complete the circuit diagram to show how a transistor switch can be used to inter<br>the Schmitt Inverter to the bulb. | rface<br>[3]                     |

|-------------|------------------------------------------------------------------------------------------------------------------------|----------------------------------|

|             | 9V<br>~                                                                                                                |                                  |

| fron<br>Sch | mitt — —                                                                                                               |                                  |

|             | о                                                                                                                      |                                  |

| (ii)        | A thyristor is often used as an interface device. Why is it <b>not</b> suitable in this system                         | m?<br>[1]                        |

|             | Sign<br>fror<br>Sch<br>Invo                                                                                            | Signal from Schmitt Inverter  OV |

5. An electronic system has two input sensors A and B, and three outputs P, Q and R. The truth table showing how the input sensors control the outputs is shown below.

| В | A | P | Q | R |

|---|---|---|---|---|

| 0 | 0 | 1 | 1 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 0 |

| (a) | Which of the follow                      | ving expressions cor | rectly describes t      | he <b>P</b> output?      | [1]         |

|-----|------------------------------------------|----------------------|-------------------------|--------------------------|-------------|

|     | $\mathbf{A}$                             | NOT A                | В                       | NOT B                    |             |

|     | Answer                                   |                      |                         |                          |             |

| (b) | Which of the follow                      | ing expressions cor  | rectly describes t      | he <b>Q</b> output?      | [1]         |

|     | A AND B                                  | A OR B               | A NAND I                | B A NOR B                |             |

|     | Answer                                   |                      |                         |                          |             |

| (c) | Complete the follow using a single logic | 0 0                  | w how the <b>R</b> outp | out can be obtained      | [1]         |

|     |                                          | A ∘<br>B ∘           | ∞ R                     |                          |             |

| (d) | Another electronic devices from input    | •                    | emory IC rather         | than logic gates to con- | trol output |

|     | The memory IC has                        | 4 address pins and   | 8 data pins.            |                          |             |

|     | (i) How many ou                          | itputs can be connec | cted to the memor       | ry IC?                   | [1]         |

|     | (ii) How many m                          | emory locations are  | there on the men        | nory IC?                 | [1]         |

(294-02)

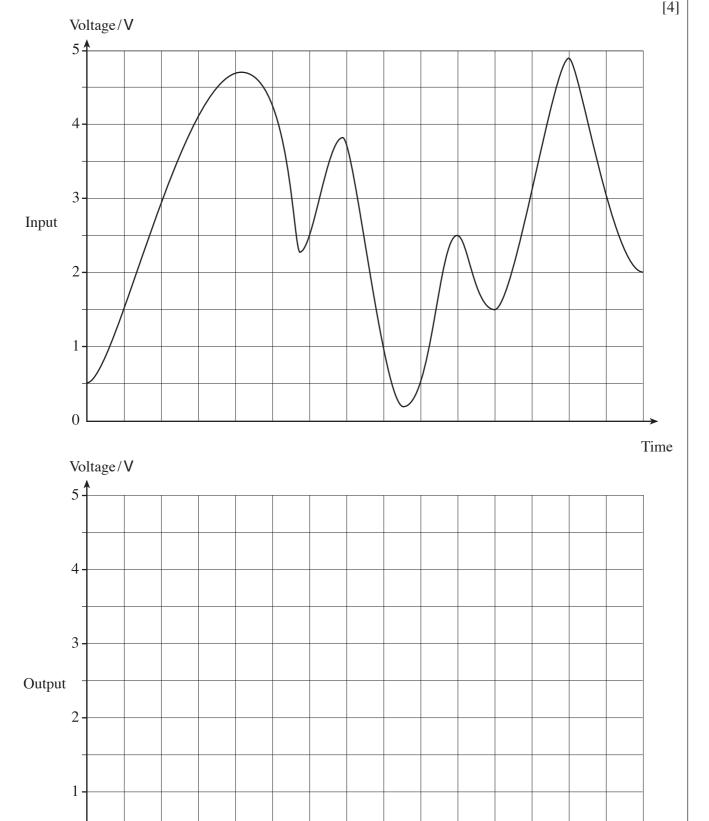

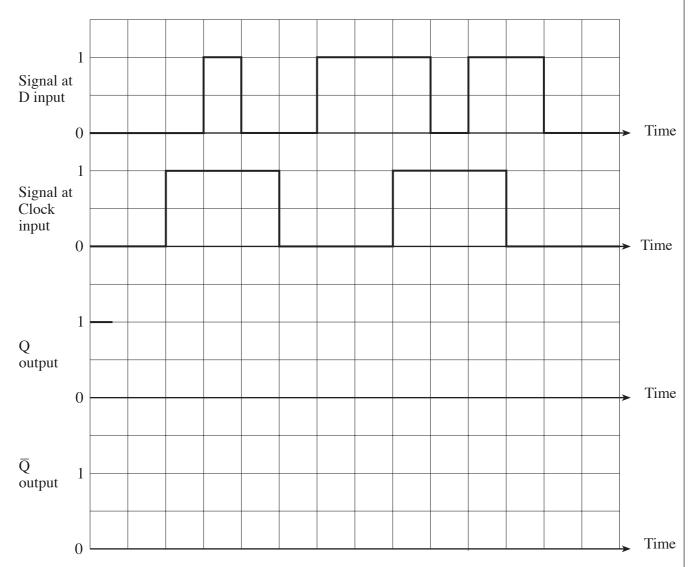

**6.** (a) The D-type flip-flop can be used for data transfer, under the control of the clock. The D-type flip-flop is rising-edge triggered.

The signal shown in the first graph is sent into the D input.

The second graph shows the pulses sent into the clock input.

Use the axes provided to draw the signals at the Q and  $\overline{Q}$  outputs.

The Q output is initially at logic 1.

[3]

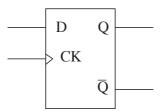

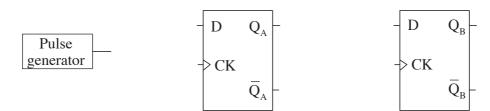

- (b) A binary counter can be built from a series of D-type flip-flops, or can be obtained as a dedicated counter IC.

- (i) The following diagram shows a pulse generator and two **rising-edge** triggered D-type flip-flops

Draw on the diagram the connections required to make a 2-bit up-counter, connected to the pulse generator. [3]

(ii) The graph shows clock pulses applied to the 2-bit up-counter. Use the axes provided to draw the signals which would appear at the outputs of the two flip-flops. [3] Initially the  $Q_{\scriptscriptstyle A}$  output and the  $Q_{\scriptscriptstyle B}$  output are both at logic 0.

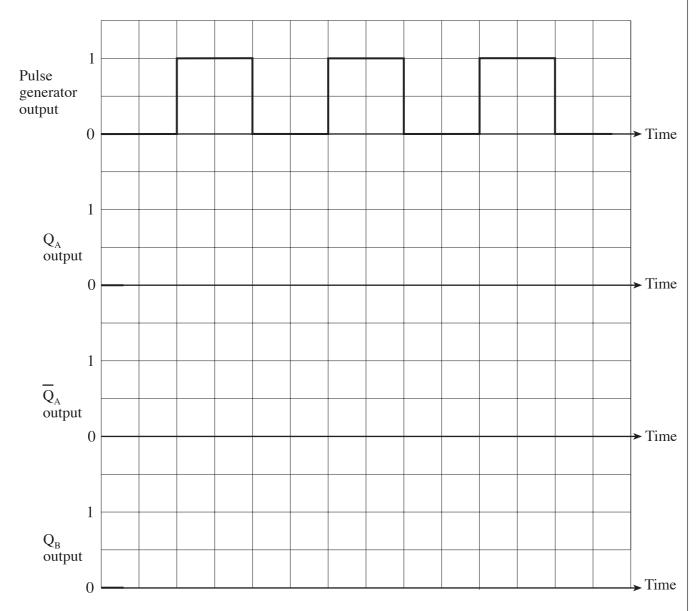

(c) The next diagram shows a counter IC, used to control a lighting sequence.

The sequence is given in the table.

| Pulse              | Lamp State |     |     |  |  |

|--------------------|------------|-----|-----|--|--|

| number             | Z          | Y   | X   |  |  |

| 0                  | Off        | Off | Off |  |  |

| 1                  | Off        | Off | On  |  |  |

| 2                  | Off        | On  | Off |  |  |

| 3                  | Off        | On  | On  |  |  |

| 4                  | On         | Off | Off |  |  |

| 5                  | On         | Off | On  |  |  |

| 6                  | Off        | Off | Off |  |  |

| 7                  | Off        | Off | On  |  |  |

| Sequence continues |            |     |     |  |  |

A lamp is switched on when the corresponding counter output is logic 1.

A partly completed circuit diagram is shown below.

Complete the circuit diagram by adding suitable connections from the counter to the AND gate. [2]