| Candidate<br>Name | - 11 |   |

|-------------------|------|---|

|                   |      | 0 |

### General Certificate of Secondary Education

294/01

# ELECTRONICS MODULE TEST E2 FOUNDATION TIER

P.M. FRIDAY, 11 January 2008 (45 minutes)

For Examiner's use only

#### ADDITIONAL MATERIALS

In addition to this examination paper you may need a calculator.

#### INSTRUCTIONS TO CANDIDATES

Write your name, centre number and candidate number in the spaces at the top of this page.

Answer all the questions in the spaces provided in this booklet.

#### INFORMATION FOR CANDIDATES

The number of marks is given in brackets at the end of each question or part-question.

No certificate will be awarded to a candidate detected in any unfair practice during the examination.

## Answer all questions.

**1.** There are three types of electronic subsystems, known as *Input*, *Processing* and *Output*.

Here are three subsystems:

| Subsystem   | Type (Input, Processing, or Output) |

|-------------|-------------------------------------|

| Buzzer      |                                     |

| Switch Unit |                                     |

| Latch       |                                     |

For each one, decide which type it is.

Add the word *Input*, *Processing* and *Output* to show what you have decided.

[3]

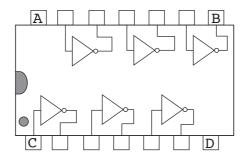

2. Here is the pin-out diagram for an IC (integrated circuit).

| (a) | How many logic gates are in this IC? |                                         |

|-----|--------------------------------------|-----------------------------------------|

| (u) | now many logic gates are in this ic. | *************************************** |

(b) How many inputs does each gate have?

(c) Which pin, A, B, C or D, is pin 1 of this IC?

(d) Choose the type of logic gate found on this IC from the following list:

AND OR NOT NAND NOR

Answer ......[4]

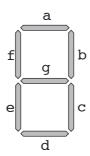

3. The diagram shows the arrangement of the LEDs in a seven-segment display.

Complete the following table.

[3]

|   | Segment |   |   |   |   |   | Number<br>Displayed |

|---|---------|---|---|---|---|---|---------------------|

| a | b       | c | d | e | f | g |                     |

| 1 | 1       | 0 | 1 | 1 | 0 | 1 |                     |

| 1 | 0       | 1 | 1 | 0 | 1 | 1 |                     |

|   |         |   |   |   |   |   | 0                   |

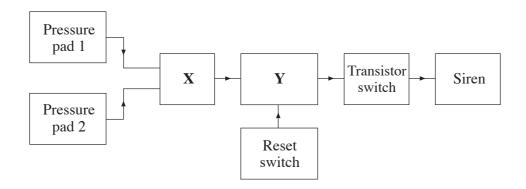

**4.** Here is the block diagram for a burglar alarm.

The siren sounds if someone stands on either pressure pad. It then stays on until the reset switch is pressed.

(a) What type of logic gate is required in block X? [1]

Answer .....

(b) Which one of the following subsystems is used for block Y? [1]

latch monostable counter AND gate

Answer .....

(c) What is the job of the transistor switch in this system?

[1]

Choose **one** of the following answers.

- **A.** It makes the siren pulse on and off, over and over again.

- **B.** It allows a small current from block **Y** to control a large current through the siren.

- C. It keeps the siren switched on for a certain length of time and then switches it off automatically.

- **D.** It protects the circuit from damaging voltages (back e.m.f.) when the siren switches off.

| Answer |  |  |

|--------|--|--|

# **BLANK PAGE**

(294-01) **Turn over.**

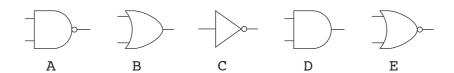

# **5.** (a) Here are five logic gate symbols:

Which symbol, A, B, C, D or E, is the symbol for:

(i) a NOT gate; [1]

(ii) an OR gate; [1]

(iii) a NAND gate? [1]

(b) Here are five truth tables:

| <b>A.</b> | Inp | Inputs |   |  |

|-----------|-----|--------|---|--|

|           | A   | В      | Q |  |

|           | 0   | 0      | 0 |  |

|           | 0   | 1      | 1 |  |

|           | 1   | 0      | 1 |  |

|           | 1   | 1      | 1 |  |

| В. | Inputs | Output |

|----|--------|--------|

|    | A      | Q      |

|    | 0      | 1      |

|    | 1      | 0      |

| C. | Inp | Output |   |

|----|-----|--------|---|

|    | A   | В      | Q |

|    | 0   | 0      | 1 |

|    | 0   | 1      | 1 |

|    | 1   | 0      | 1 |

|    | 1   | 1      | 0 |

| D. | Inp | Inputs |   |  |

|----|-----|--------|---|--|

|    | A   | В      | Q |  |

|    | 0   | 0      | 1 |  |

|    | 0   | 1      | 0 |  |

|    | 1   | 0      | 0 |  |

|    | 1   | 1      | 0 |  |

| Inputs |   | Output |

|--------|---|--------|

| A      | В | Q      |

| 0      | 0 | 0      |

| 0      | 1 | 0      |

| 1      | 0 | 0      |

| 1      | 1 | 1      |

Which table, A, B, C, D or E, is the truth table for:

(i) a NOT gate; [1]

E.

(ii) an OR gate; [1]

(iii) a NAND gate? [1]

[3]

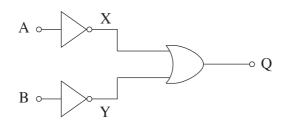

(c) (i) Complete the truth table for the following logic system:

| A | В | X | Y | Q |

|---|---|---|---|---|

| 0 | 0 |   |   |   |

| 0 | 1 |   |   |   |

| 1 | 0 |   |   |   |

| 1 | 1 |   |   |   |

(ii) Name the single logic gate which produces the same effect as this logic system.

.....[1]

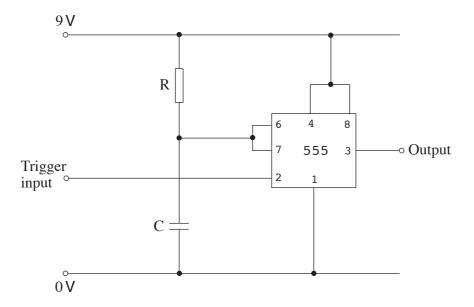

**6.** (a) The circuit diagram shows a resistor and a capacitor used with a 555 timer IC in a monostable circuit.

Here are four resistor/capacitor sets.

| Set | Resistor | Capacitor |

|-----|----------|-----------|

| A   | 10kΩ     | 22 µ F    |

| В   | 10kΩ     | 220 µ F   |

| С   | 100kΩ    | 22μF      |

| D   | 100kΩ    | 220µF     |

Which one will produce the longest time delay? [1]

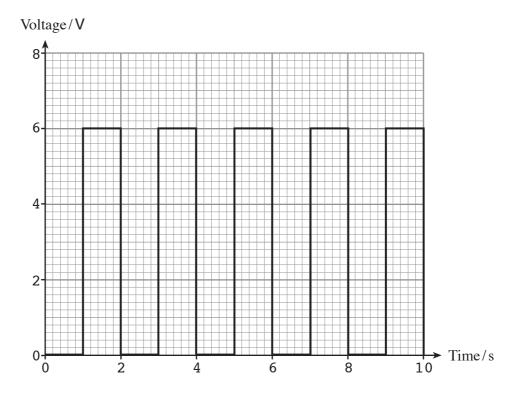

(b) Here is the signal produced by an **astable** circuit.

What is:

- (i) the amplitude of the signal; [1]

- (ii) the period of the signal? [1]

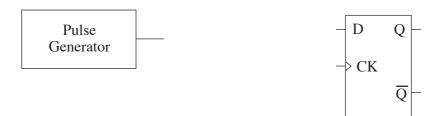

7. The following diagram shows a pulse generator and a **rising-edge**-triggered D-type flip-flop.

- (a) Draw on the diagram the **two** connections required to convert the D-type into a one-bit counter, connected to the pulse generator. [2]

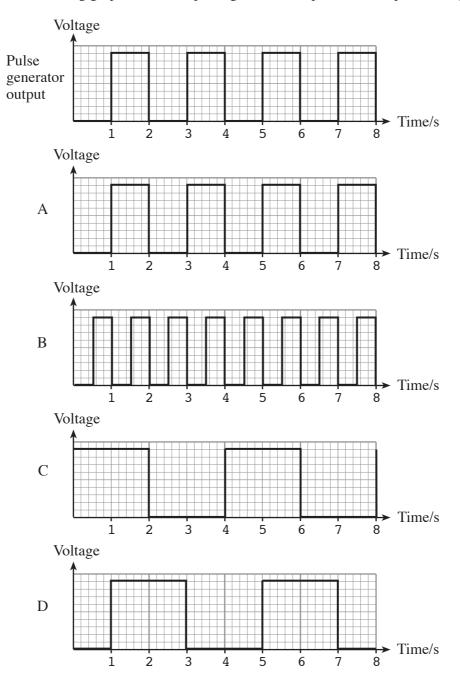

- (b) The following graphs show the pulse generator output, and four possible signals.

Which graph shows the correct output from Q?

[1]

Answer .....

**8.** An electronic system has two input sensors, A and B, and three outputs X, Y and Z. The truth table showing how the input sensors control the outputs is shown below.

| A | В | X | Y | Z |

|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 1 |

| 1 | 1 | 1 | 0 | 0 |

| (a) | Which of the following expressions correctly describes the X output?     |           |                  | ibes the X output? | [1]                        |                |

|-----|--------------------------------------------------------------------------|-----------|------------------|--------------------|----------------------------|----------------|

|     |                                                                          | A         | NOT A            | В                  | NOT B                      |                |

|     | Answer                                                                   |           |                  |                    |                            |                |

| (b) | (b) Which of the following expressions correctly describes the Y output? |           |                  |                    | [1]                        |                |

|     |                                                                          | A         | NOT A            | В                  | NOT B                      |                |

|     | Answer                                                                   |           |                  |                    |                            |                |

| (c) | Complete the                                                             | following | g diagram to sho | w how the          | Z output can be obtained u | using a single |

logic gate.

[1]

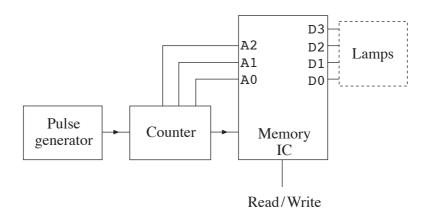

9. The block diagram shows how a disco light sequence can be generated using a memory IC.

The memory stores the following data:

| A2 | A1 | A0 | D3    | D2 | D1 | D0 |

|----|----|----|-------|----|----|----|

| 0  | 0  | 0  | 0     | 1  | 0  | 1  |

| 0  | 0  | 1  | 1     | 0  | 1  | 0  |

| 0  | 1  | 0  | 1     | 1  | 1  | 0  |

| 0  | 1  | 1  | 0     | 1  | 1  | 1  |

| 1  | 0  | 0  | 1     | 1  | 1  | 1  |

| 1  | 0  | 1  | Reset |    |    |    |

| <i>(a)</i> | How many lamps can be controlled separately by this system?                                                                                                                                |      |                                  |      |                |                   | [1]   |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------------------|------|----------------|-------------------|-------|

| (b)        | How many separate steps (patterns) are stored in this sequence?<br>Choose your answer from the following options:                                                                          |      |                                  |      |                |                   | [1]   |

|            | A. 3                                                                                                                                                                                       | B. 4 | C. 5                             | D. 6 | E. 8           | F. 16             |       |

|            | Answer                                                                                                                                                                                     |      |                                  |      |                |                   |       |

| (c)        | This memory IC has 3 address pins, <b>A2</b> , <b>A1</b> and <b>A0</b> . What is the maximum number of steps that can be stored in this IC? Choose your answer from the following options: |      |                                  |      |                |                   | [1]   |

|            | A. 3                                                                                                                                                                                       | B. 4 | C. 5                             | D. 6 | E. 8           | F. 16             |       |

|            | Answer                                                                                                                                                                                     |      |                                  |      |                |                   |       |

| (d)        |                                                                                                                                                                                            |      | n be generated<br>using the memo |      | system instead | of the memory IC. | [1]   |

|            |                                                                                                                                                                                            |      |                                  |      |                |                   | ••••• |

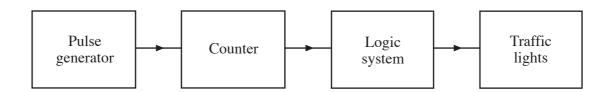

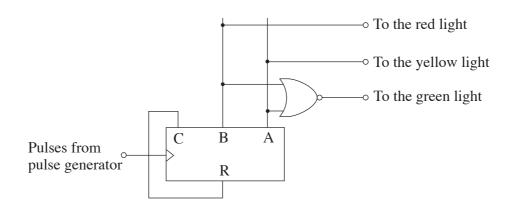

10. This is the block diagram for a set of traffic lights for a model village.

The circuit diagram for the counter is shown below.

The table shows the possible output states for the counter.

| Pulse  | Counter outputs |   |   | Traffic lights |              |             |  |

|--------|-----------------|---|---|----------------|--------------|-------------|--|

| number | C               | В | A | Red light      | Yellow light | Green light |  |

| 0      | 0               | 0 | 0 |                |              |             |  |

| 1      | 0               | 0 | 1 |                |              |             |  |

| 2      | 0               | 1 | 0 |                |              |             |  |

| 3      | 0               | 1 | 1 |                |              |             |  |

| 4      | 1               | 0 | 0 | Reset          |              |             |  |

Use the counter outputs to decide what signals are sent to the traffic lights.

**Complete the table** to show whether logic 0 or logic 1 signals are sent to the red, yellow and green lights. [4]