| Candidate | Centre | Candidate |  |

|-----------|--------|-----------|--|

| Name      | Number | Number    |  |

|           |        | 0         |  |

# **GCSE**

294/01

# ELECTRONICS MODULE TEST E2 FOUNDATION TIER

P.M. FRIDAY, 6 June 2008 45 minutes

For Examiner's use only

### ADDITIONAL MATERIALS

In addition to this examination paper you may need a calculator.

### INSTRUCTIONS TO CANDIDATES

Write your name, centre number and candidate number in the spaces at the top of this page. Answer **all** the questions in the spaces provided in this booklet.

## INFORMATION FOR CANDIDATES

The number of marks is given in brackets at the end of each question or part-question.

### Answer all questions.

1. There are three types of electronic subsystem, known as *Input*, *Process* and *Output*.

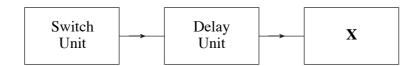

Here is the block diagram for a door-entry alarm. It warns a shopkeeper when someone enters the shop.

|     | (a) | What kind of sub-s  | vstem is the | Switch Unit - In | mut Process of   | or Output?  |

|-----|-----|---------------------|--------------|------------------|------------------|-------------|

| - ( | (u) | What Killy of Sub-S | ystem is the | Switch Omt – Ii  | ipui, i iocess i | ու Ծաւթաւ ։ |

.....[1]

(b) What kind of sub-system is the Delay Unit – Input, Process or Output?

.....[1]

(c) Choose a suitable device for block  $\mathbf{X}$  from the following list of sub-systems:

Comparator AND gate Buzzer Pulse Generator ......[1]

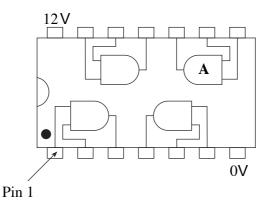

2. The diagram shows the pin-out for an IC (integrated circuit).

- (a) How many logic gates are in this IC?

- (b) How many inputs does each gate have?

- (c) Pin 1 is labelled.

- (i) What is the pin number for the 0 V pin?

- (ii) What is the pin number for the output of gate A? [4]

3. The diagram shows the arrangement of the LEDs in a seven-segment display.

Complete the following table.

|   |   | Number |   |   |   |   |           |  |

|---|---|--------|---|---|---|---|-----------|--|

| a | b | с      | d | e | f | g | Displayed |  |

| 1 | 1 | 1      |   |   |   |   | 7         |  |

| 1 | 1 | 1      | 1 | 0 | 0 | 1 |           |  |

[2]

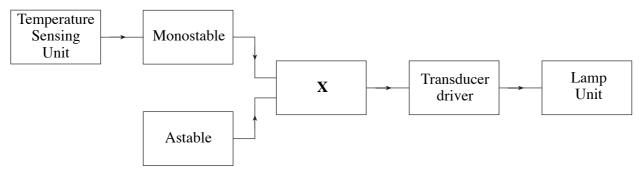

**4.** Here is the block diagram for a freezer alarm.

The lamp does not light when the freezer is cold enough.

The lamp flashes on and off repeatedly when the freezer is too hot.

The monostable outputs a logic 1 signal for 30 s when the freezer gets too hot.

(a) What type of logic gate is required in block X?

Answer .....

(b) What is the job of the astable in this system?

Choose one of the following answers:

- **A.** It makes the Lamp Unit pulse on and off over and over again.

- **B.** It outputs a steady logic 1 signal when the freezer gets too hot.

- C. It keeps the Lamp Unit switched on for 30 s and then switches it off automatically.

- **D.** It buffers the output of the monostable, providing enough current to light the lamp.

Answer .....

[1]

[1]

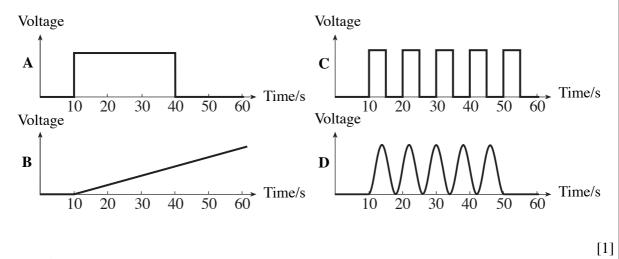

(c) The temperature in the freezer rises and triggers the monostable.

Which of the following shows the output signal from the monostable?

Answer .....

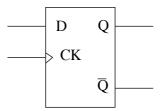

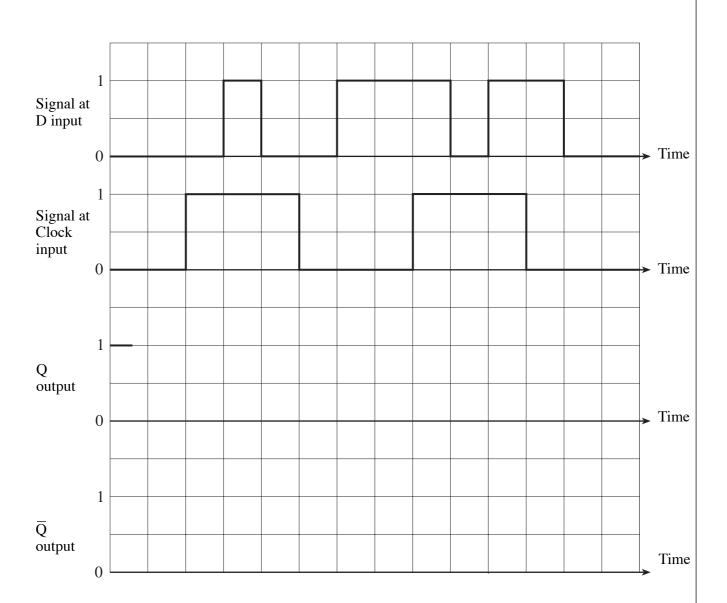

**5.** The D-type flip-flop can be used for data transfer, under the control of the clock. The D-type flip-flop is rising-edge triggered.

The signal shown in the first graph is sent into the D input. The second graph shows the pulses sent into the clock input. Use the axes provided to draw the signals at the Q and  $\overline{Q}$  outputs.

## The Q output is initially at logic 1.

[3]

(294-01)

[1]

[3]

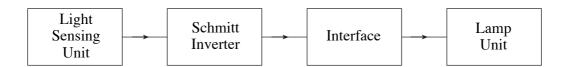

The block diagram shows the design of a security light, which turns on automatically when it gets dark.

The lamp comes on when it gets dark. Which block detects the light level?

[1]

- The Light Sensing Unit gives out a logic 0 signal in the dark.

- (i) The Schmitt Inverter inverts the signal from the Light Sensing Unit. Explain what this sentence means.

What is the other use of the Schmitt Inverter in this system? (ii) [1]

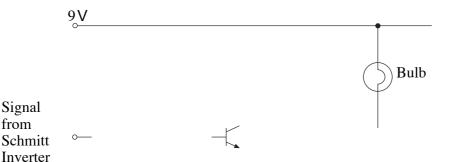

The circuit diagram shows part of the interface.

from

- Add a resistor to limit the base current into the transistor.

- (ii) Draw the connections needed to complete the circuit diagram.

0 V

A thyristor is often used as an interface device. Why is it **not** suitable in this system? [1]

[3]

[1]

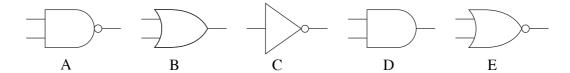

# 7. (a) Here are five logic gate symbols:

Complete the table to match the logic symbols and their names.

| Logic gate name | Correct symbol, A, B, C, D or E |

|-----------------|---------------------------------|

| AND gate        |                                 |

| NAND gate       |                                 |

| NOR gate        |                                 |

| NOT gate        |                                 |

| OR gate         |                                 |

(b) Complete the truth tables for the following logic gates:

(i) a **NOT** gate [1]

| Input | Output |

|-------|--------|

| 0     |        |

| 1     |        |

(ii) an AND gate

Inputs

Output

0

0

0

1

1

0

1

1

(294-01)

Turn over.

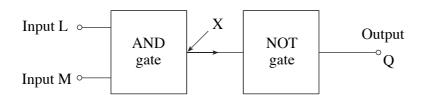

(c) A **NOT** gate and an **AND** gate are connected together as shown in the block diagram.

(i) Complete the following truth table for this system:

| L | M | X | Q |

|---|---|---|---|

| 0 | 0 |   |   |

| 0 | 1 |   |   |

| 1 | 0 |   |   |

| 1 | 1 |   |   |

| ſ |   | ٦ |

|---|---|---|

| ı | _ | ı |

(ii) Name the single logic gate which produces the same effect as this logic system.

.....[1]

8. An electronic system has two input sensors A and B, and three outputs P, Q and R. The truth table showing how the input sensors control the outputs is shown below.

| В | A | P | Q | R |

|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 | 0 |

|            |      | 1                                | 1          | 1              | 0          | 0                     | ]                 |               |

|------------|------|----------------------------------|------------|----------------|------------|-----------------------|-------------------|---------------|

| (a)        | Whic | ch of the follo                  | owing exp  | oressions corr | ectly des  | cribes the <b>P</b> o | output?           | [1]           |

|            |      |                                  | A          | NOT A          | В          | NOT B                 |                   |               |

|            | Ansv | ver                              |            | <b></b>        |            |                       |                   |               |

| <i>(b)</i> | Whic | ch of the follo                  | owing exp  | pressions corr | ectly des  | cribes the <b>Q</b>   | output?           | [1]           |

|            |      |                                  | A          | NOT A          | В          | NOT B                 |                   |               |

|            | Ansv | ver                              |            |                |            |                       |                   |               |

| (c)        |      | plete the foll<br>g a single log |            | gram to shov   | v how the  | e <b>R</b> output car | n be obtained     | [1]           |

|            |      |                                  | _          | A              |            |                       |                   |               |

|            |      |                                  | ]          | В              |            | ⊸ R                   |                   |               |

| (d)        |      | ther electron                    |            |                | mory IC    | rather than           | logic gates to c  | ontrol output |

|            | The  | memory IC h                      | as 4 addre | ess pins and 8 | 3 data pin | s.                    |                   |               |

|            | (i)  | How many                         | separate o | output device  | s can be o | connected to          | the memory IC?    |               |

|            |      |                                  |            |                |            |                       |                   | [1]           |

|            | (ii) | Which of th                      | ne followi | ng gives the 1 | number o   | f memory loc          | cations on the me | emory IC?     |

|            |      |                                  | 4          | 8              | 12         | 16                    |                   |               |

|            |      | Answer                           |            |                |            |                       |                   | [1]           |

|            |      |                                  |            |                |            |                       |                   |               |

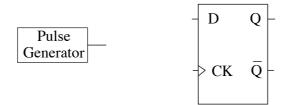

- **9.** A binary counter can be built from a series of D-type flip-flops, or can be obtained as a dedicated counter IC.

- (a) The diagram shows a pulse generator and a **rising-edge** triggered D-type flip-flop.

Draw on the diagram the **two** connections required to convert the D-type into a one-bit counter, connected to the pulse generator. [2]

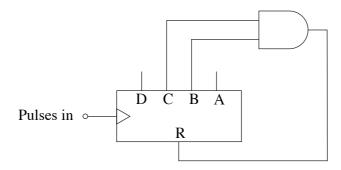

(b) The next diagram shows a counter IC, with its reset controlled by an AND gate.

Complete the table to show the sequence of outputs produced, including the effect of the AND gate. [3]

| Pulse  | Counter outputs |   |   |  |  |  |

|--------|-----------------|---|---|--|--|--|

| number | C               | В | A |  |  |  |

| 0      | 0               | 0 | 0 |  |  |  |

| 1      |                 |   |   |  |  |  |

| 2      |                 |   |   |  |  |  |

| 3      |                 |   |   |  |  |  |

| 4      |                 |   |   |  |  |  |

| 5      |                 |   |   |  |  |  |

| 6      |                 |   |   |  |  |  |

| 7      |                 |   |   |  |  |  |