| Candidate Name | Centre Number | Candidate Number |

|----------------|---------------|------------------|

|                |               |                  |

### WELSH JOINT EDUCATION COMMITTEE

**General Certificate of Secondary Education**

CYD-BWYLLGOR ADDYSG CYMRU

Tystysgrif Gyffredinol Addysg Uwchradd

294/01

#### **ELECTRONICS**

### **MODULE TEST E2**

#### FOUNDATION TIER

P.M. FRIDAY, 12 January 2007

(45 minutes)

For Examiner's use only

# **ADDITIONAL MATERIALS**

In addition to this examination paper you may need a calculator.

### INSTRUCTIONS TO CANDIDATES

Write your name, centre number and candidate number in the spaces at the top of this page.

Answer **all** the questions in the spaces provided in this booklet.

# INFORMATION FOR CANDIDATES

The number of marks is given in brackets at the end of each question or part-question.

No certificate will be awarded to a candidate detected in any unfair practice during the examination.

# Answer all questions.

1. Here is a list of electronic sub-systems:

|       | motor                 | moisture sensor         | MOSFET                  | push switch   |

|-------|-----------------------|-------------------------|-------------------------|---------------|

| Inser | t the correct sub-sys | stem to complete the fo | llowing statement       | s.            |

| (a)   | Α                     | is                      | an <b>analogue</b> inpu | t sub-system; |

| (b)   | A                     | is                      | a processing sub-       | system;       |

| (c)   | A                     | is                      | an output sub-sys       | tem.          |

|       |                       |                         |                         |               |

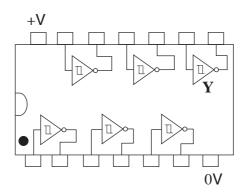

2. The pin-out diagram below shows a logic IC.

|     |                                                                        | [1] |

|-----|------------------------------------------------------------------------|-----|

|     | OR NAND NOT SCHMITT INVERTER                                           |     |

|     | Choose from the following list:                                        |     |

| (e) | What is the name given to the type of logic gate contained in this IC? |     |

| (d) | Give the number of the pin connected to the output of gate Y           | [1] |

| (c) | Label pin 1 with the number 1.                                         | [1] |

| (b) | How many inputs does each gate have?                                   | [1] |

| (a) | How many logic gates are contained in this IC?                         | [1] |

|     |                                                                        |     |

3. The diagram shows the arrangement of the LEDs in a seven-segment display.

Complete the following table, which shows the number/letter displayed when different segments are lit.

| Segment |   |   |   | Letter/Number<br>displayed |   |   |   |

|---------|---|---|---|----------------------------|---|---|---|

| a       | b | С | d | e                          | f | g |   |

| 1       | 0 |   |   |                            |   |   | F |

|         |   |   |   |                            |   |   | 3 |

| 0       | 1 | 1 | 0 | 1                          | 1 | 1 |   |

[3]

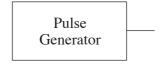

**4.** The diagram shows a pulse generator and a D-type flip-flop.

(a) The D-type must be connected so that it performs a *divide-by-two* action on pulses from the pulse generator.

Draw the two connections needed to do this.

[2]

(b) The frequency of the signal at the Q output is 200 Hz.

What is the frequency of the pulse generator?

[1]

(294/01)

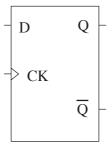

**5.** Here is the diagram for an astable circuit based on a 555 timer IC.

- (a) Name the component labelled **P**. [1]

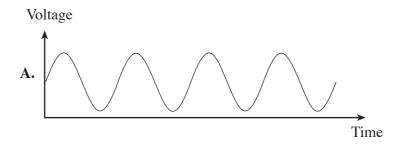

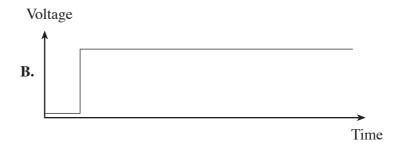

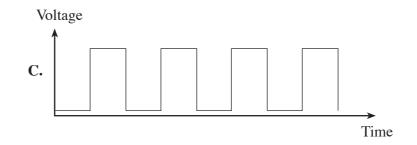

- (b) Which of the following is the output waveform produced by an astable circuit?

Answer .....

[1]

| (c) | (i)  | The value of $\mathbf{R}_2$ is increased. What happens to the frequency of the output signal?         |

|-----|------|-------------------------------------------------------------------------------------------------------|

|     | (ii) | The value of component $\mathbf{P}$ is increased. What happens to the frequency of the output signal? |

|     |      | [2]                                                                                                   |

(294/01) **Turn over.**

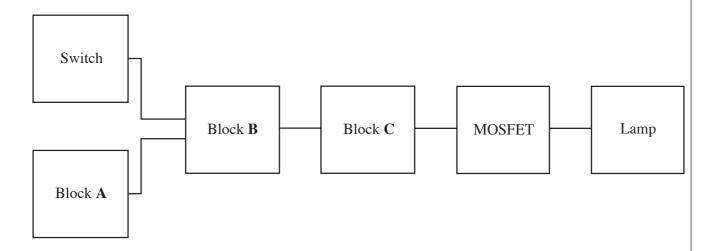

**6.** (a) Here is a system that controls a lamp on a stairway. The lamp comes on when the switch is pressed *but only* if it is dark. The lamp switches off automatically after 1 minute.

You can choose any of the following sub-systems to use for blocks A, B and C:-

Temperature sensing unit

Light sensing unit

OR gate

Delay unit

Pulse unit

AND gate

Which sub-system is

- (i) a suitable unit for block A?

- (ii) a suitable unit for block **B**?

- (b) The above system is an example of electronics being used in the home.

- (i) Describe **another** use of electronics in the home.

- (ii) Describe **one** benefit of electronics to a hospital patient.

[2]

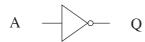

- 7. (a) Write the name of each logic gate in the space provided and complete the truth tables.

- (i) Gate 1

| A | Q |

|---|---|

| 0 |   |

| 1 |   |

Name of gate:

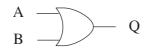

(ii) Gate 2

| A | В | Q |

|---|---|---|

| 0 | 0 |   |

| 0 | 1 |   |

| 1 | 0 |   |

| 1 | 1 |   |

Name of gate: [4]

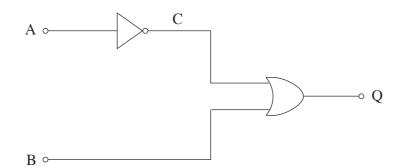

(b) Complete the truth table for the following logic system.

| A | В | С | Q |

|---|---|---|---|

| 0 | 0 |   |   |

| 0 | 1 |   |   |

| 1 | 0 |   |   |

| 1 | 1 |   |   |

[2]

**8.** A logic system has two input sensors A and B, and three outputs P, Q and R. The truth table showing how the input sensors control the outputs is shown below.

| В | A | P | Q | R |

|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 | 0 |

| (a)        | (i)   | Look at the P output. Which type of logic gate will provide this?                                                                                                   |     |

|------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|            |       | Logic gate is                                                                                                                                                       |     |

|            | (ii)  | Look at the Q output. Which type of logic gate will provide this?                                                                                                   |     |

|            |       | Logic gate is                                                                                                                                                       |     |

|            | (iii) | Look at the R output. It is the inverse of one of the inputs. Write down an expression to describe this output.                                                     |     |

|            |       | R =                                                                                                                                                                 |     |

|            |       |                                                                                                                                                                     | [3] |

| <i>(b)</i> |       | have a selection of AND, OR, NOT, NOR and NAND gates available.  v a labelled diagram to show how the logic system can be made.                                     |     |

|            | A     | -∞ P                                                                                                                                                                |     |

|            |       |                                                                                                                                                                     |     |

|            |       | Q                                                                                                                                                                   |     |

|            |       |                                                                                                                                                                     |     |

|            | В     | o—                                                                                                                                                                  |     |

|            |       | —∘ R                                                                                                                                                                |     |

|            |       |                                                                                                                                                                     | [3] |

| (c)        | adva  | emory IC could be used to give the same output as the logic system. Give ntage, other than cost, of designing an electronic system using a memory IC instead gates. |     |

| •••••      |       |                                                                                                                                                                     |     |

|            |       |                                                                                                                                                                     |     |

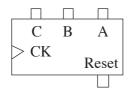

**9.** A company packs DVDs into boxes, five to a box.

Part of the packing system is shown in the following block diagram.

- The counting sub-system contains a 3-bit binary counter and an AND gate

- The system must reset when the **fifth** DVD passes the light sensor

- Taking the reset pin to logic 1 resets the counter

- Bit A of the counter is the least significant bit

- The counter is initially reset

- (a) Complete the diagram below to show how the AND gate is connected to the counter to allow it to reset correctly.

[3]

(b) Why is a Schmitt Inverter needed in **this** system? [1]