Surname

Centre Number Candidate Number

Other Names

# GCSE

4162/01

S16-4162-01

## ELECTRONICS UNIT E2: Paper replacement test

P.M. TUESDAY, 21 June 2016

1 hour

| For Examiner's use only               |    |  |  |  |  |

|---------------------------------------|----|--|--|--|--|

| Question Maximum Mark<br>Mark Awarded |    |  |  |  |  |

| 1.                                    | 4  |  |  |  |  |

| 2.                                    | 3  |  |  |  |  |

| 3.                                    | 2  |  |  |  |  |

| 4.                                    | 4  |  |  |  |  |

| 5.                                    | 3  |  |  |  |  |

| 6.                                    | 2  |  |  |  |  |

| 7.                                    | 3  |  |  |  |  |

| 8.                                    | 3  |  |  |  |  |

| 9.                                    | 2  |  |  |  |  |

| 10.                                   | 3  |  |  |  |  |

| 11.                                   | 3  |  |  |  |  |

| 12.                                   | 3  |  |  |  |  |

| 13.                                   | 5  |  |  |  |  |

| 14.                                   | 5  |  |  |  |  |

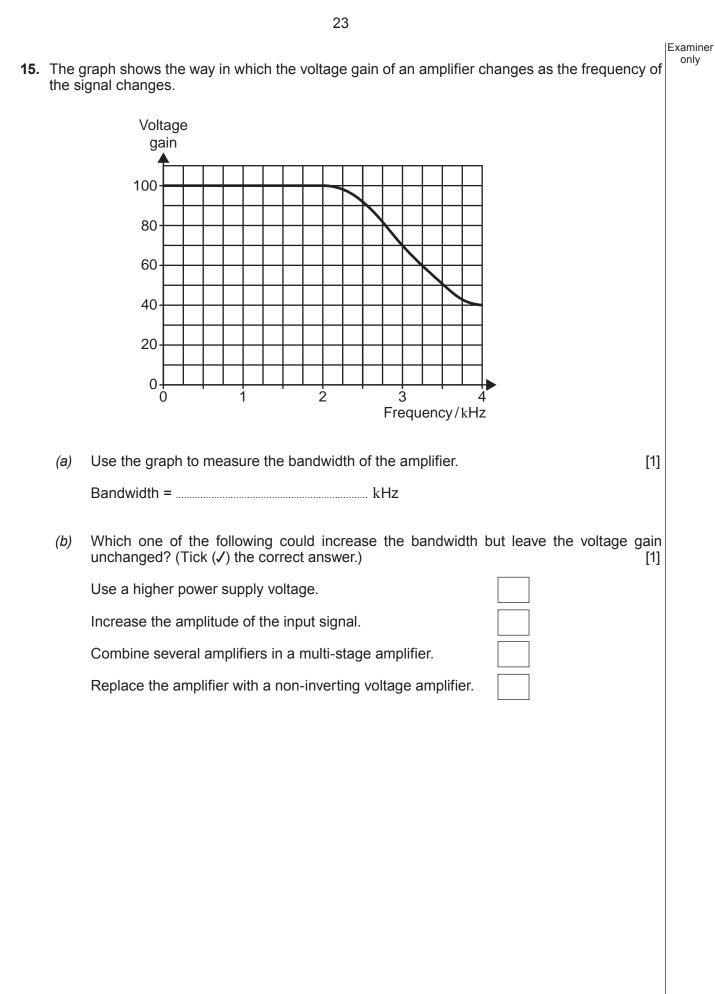

| 15.                                   | 2  |  |  |  |  |

| 16.                                   | 2  |  |  |  |  |

| 17.                                   | 2  |  |  |  |  |

| 18.                                   | 3  |  |  |  |  |

| 19.                                   | 6  |  |  |  |  |

| Total                                 | 60 |  |  |  |  |

### ADDITIONAL MATERIALS

In addition to this paper you may require a calculator and a ruler.

### **INSTRUCTIONS TO CANDIDATES**

Use black ink or black ball-point pen.

Write your name, centre number and candidate number in the spaces at the top of this page.

Answer **all** questions in the spaces provided in this booklet.

### INFORMATION FOR CANDIDATES

The number of marks is given in brackets at the end of each question or part-question.

#### **INFORMATION SHEET FOR UNIT E2**

This information may be of use in answering the questions.

## 1. Resistor Colour

| Codes |  |

|-------|--|

|-------|--|

| BLACK  | 0 | GREEN  | 5 |

|--------|---|--------|---|

| BROWN  | 1 | BLUE   | 6 |

| RED    | 2 | VIOLET | 7 |

| ORANGE | 3 | GREY   | 8 |

| YELLOW | 4 | WHITE  | 9 |

The fourth band colour gives the tolerance as follows:

| GOLD | ± | 5% |

|------|---|----|

|      |   |    |

SILVER ± 10%

#### 2. Preferred Values for Resistors – E24 series

10, 11, 12, 13, 15, 16, 18, 20, 22, 24, 27, 30, 33, 36, 39, 43, 47, 51, 56, 62, 68, 75, 82, 91.

- 3. **Resistance =**  $\frac{\text{voltage}}{\text{current}}$ ; R =  $\frac{\text{V}}{\text{I}}$ .

- 4. Effective resistance, R, of two resistors  $R_1$  and  $R_2$  in series is given by  $R = R_1 + R_2$ .

- 5. Effective resistance, R, of two resistors  $R_1$  and  $R_2$  in parallel is given by  $R = \frac{R_1 R_2}{R_1 + R_2}$ .

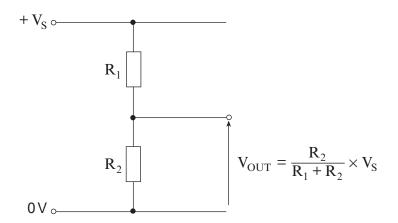

- 6. Voltage Divider

- 7. **Power =** voltage × current;  $P = VI = I^2R = \frac{V^2}{R}$ .

- 8. LED The forward voltage drop across a LED is 2 V.

- 9. NPN Transistors (i) Current gain =  $\frac{\text{Collector current}}{\text{Base current}}$ ;  $h_{FE} = \frac{I_C}{I_B}$ .

- (ii) The forward voltage drop across the base emitter junction is 0.7 V.

## 10. Amplifiers

Voltage gain: A =

$$=\frac{V_{OUT}}{V_{IN}}$$

Non-inverting amplifier:

$$A = 1 + \frac{R_F}{R_1}$$

Inverting amplifier:

$$A = -\frac{R_F}{R_{IN}}$$

Summing amplifier:

$$V_{OUT} = -R_F \left( \frac{V_1}{R_1} + \frac{V_2}{R_2} + ... \right)$$

3

4

#### Answer all questions.

1. (a) The boxes on the left give the names of two sub-systems.

The boxes on the right give descriptions of three applications.

Draw a line to link each sub-system to its correct application.

[2]

Examiner only

When a burglar alarm is switched on a warning LED flashes on and off, repeatedly.

A street light comes on when it gets dark and turns off when it gets light.

The buzzer in a shop comes on for 10 seconds when someone steps on a pad in the doorway and then goes off automatically.

Monostable

Astable

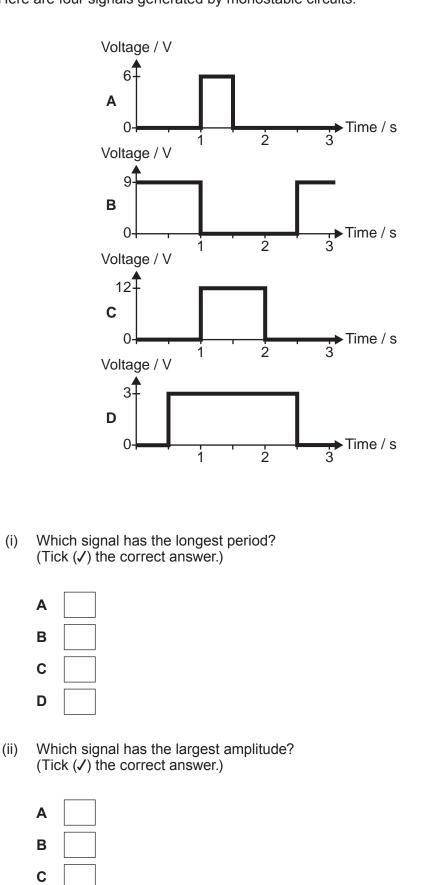

Here are four signals generated by monostable circuits.

(b)

D

Turn over.

4162 010005

[1]

[1]

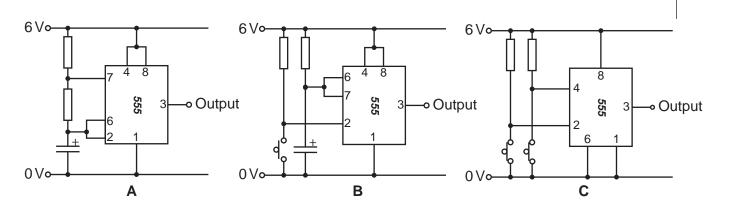

(a) One of the following circuits is an astable circuit, one a latch and one a monostable.

Which one is an astable circuit? (Tick ( $\checkmark$ ) the correct answer.)

2.

6

Examiner only

[1]

(b) Here are three astable signals.

Which has the highest frequency? (Tick (✓) the correct answer.)

(ii) What is the amplitude of signal A in volts? (Tick (✓) the correct answer.)

[1]

[1]

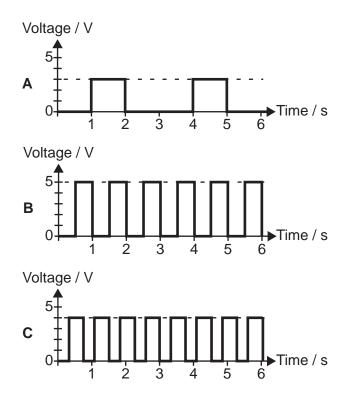

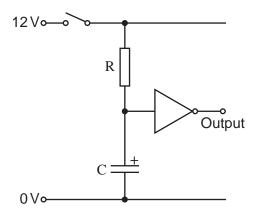

Examiner only **3.** The circuit diagram shows a time delay circuit. When the switch is closed, the output stays at a high voltage for a while and then drops to a lower value.

(a) Which one of the following sets of resistor / capacitor values keeps the output high for the longest time? (Tick (✓) the correct answer.) [1]

| Set | Resistor             | Capacitor |

|-----|----------------------|-----------|

| А   | $10\mathrm{k}\Omega$ | 220µF     |

| В   | 100 kΩ               | 220µF     |

| С   | <b>10</b> kΩ         | 22µF      |

| D   | 100 kΩ               | 22µF      |

(b) Which one of the following statements gives the **best** explanation for the purpose of the NOT gate in this circuit? (Tick (✓) the correct answer.) [1]

Without the NOT gate, the time delay would be much shorter.

It produces an analogue output voltage.

It ensures that the output current does not affect the time delay.

It inverts the signal from the switch.

Examiner only

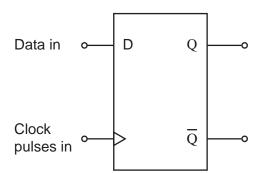

**4.** (a) Which of the following statements describes the action of the rising-edge triggered D-type [1]

When the clock signal rises from logic 0 to logic 1: the Q output copies the logic level present on the clock input. the Q output copies the logic level present on the data input. the  $\overline{Q}$  output copies the logic level present on the clock input. the  $\overline{Q}$  output copies the logic level present on the data input.

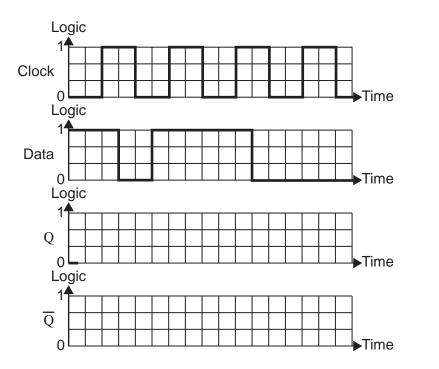

*(b)* A rising-edge triggered D-type flip-flop receives the clock and data signals shown in the graphs.

Complete the graphs to show the Q and  $\overline{Q}$  outputs.

The Q output starts at logic 0.

|Examiner

4162 010009

[3]

(4162-01)

6. The boxes on the left give the names of two interface devices.

The boxes on the right give three descriptions.

Draw a line to link each device to its correct description.

Has two fixed switching thresholds

Comparator

Has one switching threshold which can be changed easily

Schmitt trigger

Has one fixed switching threshold of  $0.7 \, \text{V}$

4162 010011

Examiner only

[2]

Examiner only

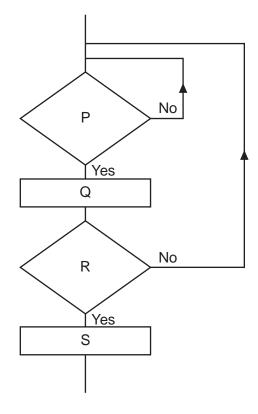

7. Here is a flowchart for part of a control system.

This part of the system:

- waits until a switch is pressed

- then it adds 1 to a variable called 'total'

- it checks to see if 'total' has reached 12

- if it has, it resets the counter

- if it has not, it goes back to check the switch again.

The flowchart contains the following four instructions:

Instruction A Is 'total' = 12? Instruction B Is the switch pressed? Instruction C Add 1 to 'total' Instruction D Reset 'total'.

(a) Which of these instructions will be found in box P?

(Tick (✓) the correct answer.)

[1]

13

(c) Which of these instructions will be found in box R?

(Tick (✓) the correct answer.)

С

D

А

В

С

D

[1]

Examiner only

| 8. | Micr | is the block diagram for a simple public address system.<br>ophone Preamplifier Mixer Power amplifier Loudspeaker<br>ophone Preamplifier Vower amplifier Course address systems<br>sub-systems used in this are:<br>er Loudspeaker Preamplifier Microphone Power amplifier | Examiner<br>only |

|----|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

|    | Whic | h sub-system:                                                                                                                                                                                                                                                              |                  |

|    | (a)  | turns sound into electrical signals; [1]                                                                                                                                                                                                                                   |                  |

|    | (b)  | boosts the current; [1]                                                                                                                                                                                                                                                    |                  |

|    | (C)  | combines the signal from a number of sources? [1]                                                                                                                                                                                                                          |                  |

14

© WJEC CBAC Ltd.

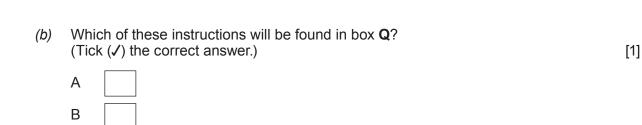

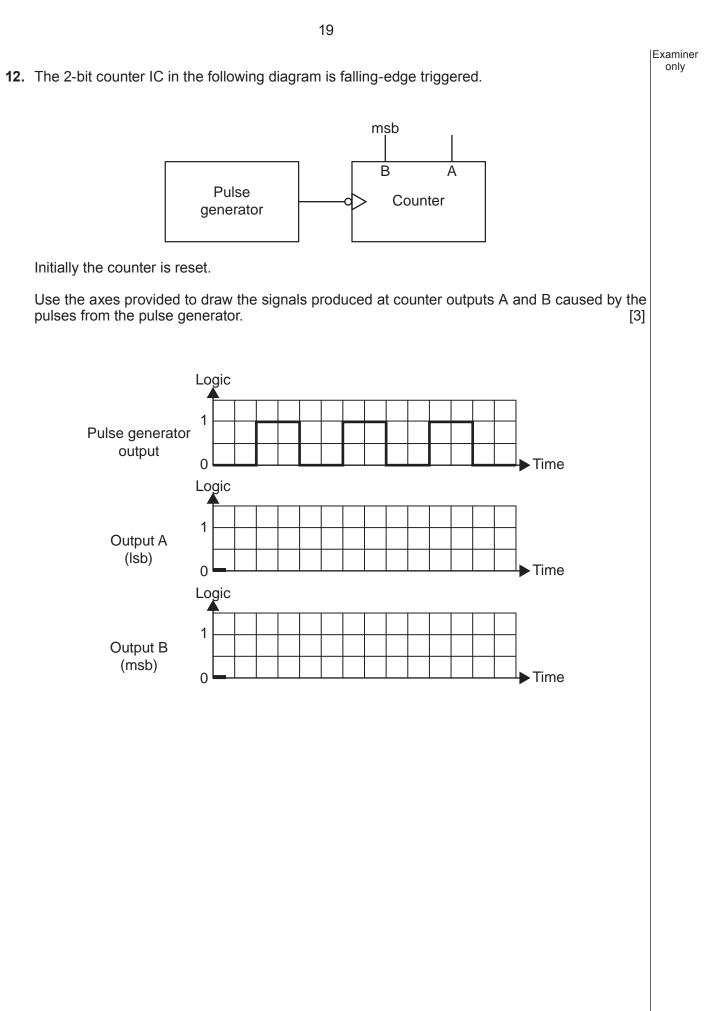

9. The diagram shows a D-type flip-flop used as a 'divide-by-two' sub-system.

The Q output generates pulses with a frequency of 20 Hz.

What is the frequency of the signals at:

| (a) | the clock input                    | <br>Hz; |

|-----|------------------------------------|---------|

| (b) | the $\overline{\mathrm{Q}}$ output | <br>Hz? |

4162 010015

[1]

[1]

Examiner only

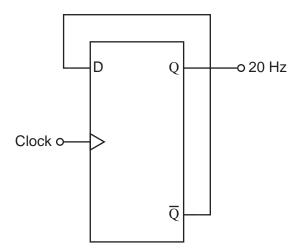

Examiner only 10. What is the voltage gain of the amplifier shown below? [1] (a) 2 mV • 30 mV Voltage gain = Which one of the following options would give the amplifier a voltage gain of 10? (Tick ( $\checkmark$ ) the correct answer.) (b) [1] Ρ O 0 + Q 0 V -**Resistor P Resistor Q** 9kΩ  $1 k\Omega$  $10 k\Omega$  $1 k\Omega$

2kΩ

$2k\Omega$

$20 \, k\Omega$

**22** kΩ

Examiner only

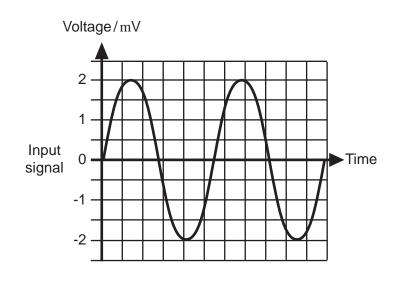

(c) The signal shown in the graph is applied to an amplifier having a voltage gain of 20.

What is the amplitude of the output signal?

[1]

..... mV

|Examiner only **11.** A light sequence controller uses a simple memory IC to control a number of LEDs. The memory IC has four address pins and three data pins. A logic 1 signal from a memory IC output causes the corresponding LED to light. A3 -o To red LED D2 A2 D1 A1 -o To yellow LED D0 HÞ A0 D С В A Pulse Memory generator Counter (0.5 Hz) Complete the statement. (a) The pulse generator has a period of ...... seconds. [1] (b) Complete the statement by circling the correct answer below: [1] 0.25 0.5 2 4 8 The pulses applied to A1 have a period of ...... seconds. (C) Which of the following statements about the memory is true? (Tick  $(\checkmark)$  the correct answer.) [1] It has 4 memory locations, each storing a 3 bit-number. It has 4 memory locations, each storing an 8 bit-number. It has 16 memory locations, each storing a 3 bit-number. It has 16 memory locations, each storing an 8 bit-number.

20

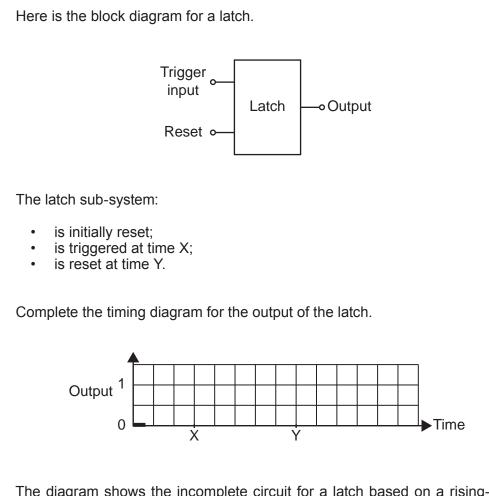

13.

(a)

Examiner only

[2]

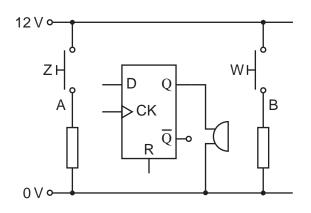

(b) The diagram shows the incomplete circuit for a latch based on a rising-edge triggered D-type flip-flop. Switch Z is used to trigger the latch. Switch W is used to reset it. The buzzer sounds when the latch is triggered.

|       | e connections are needed t<br>< (✓) the correct answer.) | to complete the circ | suit: | Examiner<br>only |

|-------|----------------------------------------------------------|----------------------|-------|------------------|

| (i)   | A must be connected to:                                  | Data input           | [1]   |                  |

|       |                                                          | Clock input          |       |                  |

|       |                                                          | Reset input          |       |                  |

|       |                                                          | 12V power rail       |       |                  |

|       |                                                          | 0 V power rail       |       |                  |

| (ii)  | B must be connected to:                                  | Data input           | [1]   |                  |

|       |                                                          | Clock input          |       |                  |

|       |                                                          | Reset input          |       |                  |

|       |                                                          | 12V power rail       |       |                  |

|       |                                                          | 0 V power rail       |       |                  |

| (iii) | D must be connected to:                                  | Data input           | [1]   |                  |

|       |                                                          | Clock input          |       |                  |

|       |                                                          | Reset input          |       |                  |

|       |                                                          | 12 V power rail      |       |                  |

|       |                                                          | 0 V power rail       |       |                  |

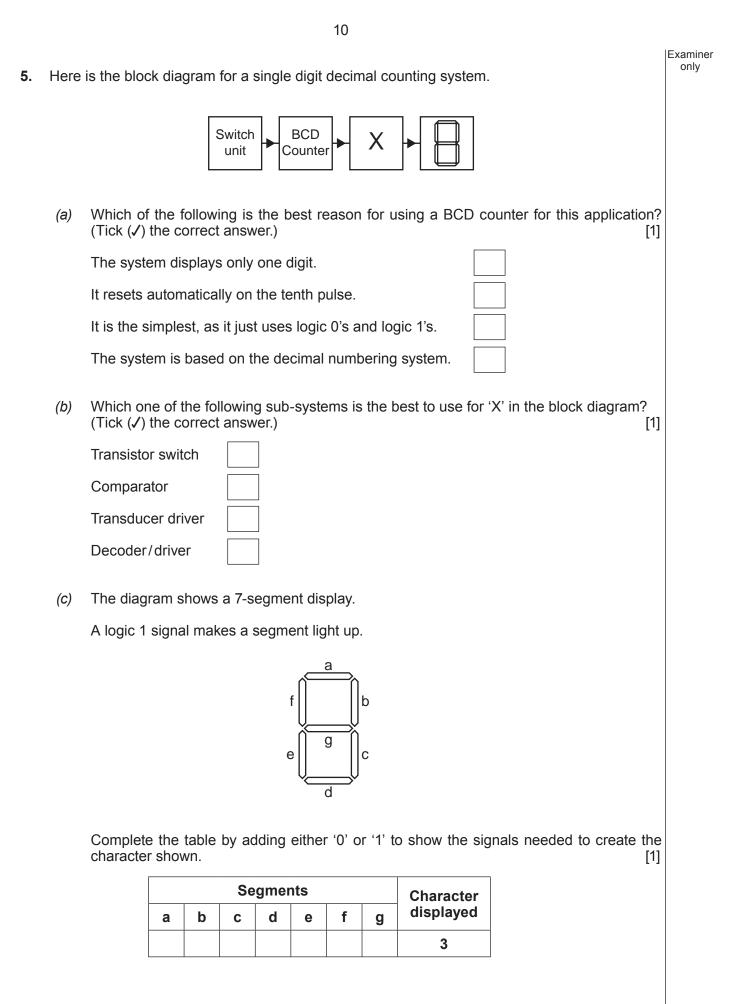

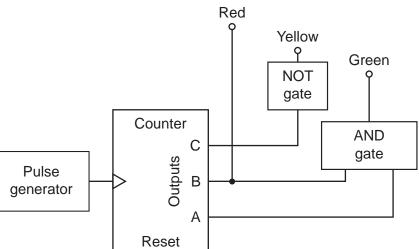

14. The diagram shows part of a light sequence controller circuit, for three LEDs.

A LED lights when it receives a logic 1 signal.

\_

Γ

The incomplete table below describes the counter outputs as more pulses arrive at its input, and the resulting states of the LEDs.

- ----

| Pulse | Οοι | inter outp | iter outputs |     | LED    |       |  |

|-------|-----|------------|--------------|-----|--------|-------|--|

|       | С   | В          | Α            | Red | Yellow | Green |  |

| None  | 0   | 0          | 0            | Off | On     | Off   |  |

| 1     | 0   | 0          | 1            |     |        |       |  |

| 2     | 0   | 1          | 0            |     |        |       |  |

| 3     |     |            |              |     |        |       |  |

| 4     |     |            |              |     |        |       |  |

(a) Which one of the following would make the counter reset on pulse 4?

(Tick (✓) the correct answer.)

Connect counter output A directly to the Reset input.

Connect counter output B directly to the Reset input.

Connect counter output C directly to the Reset input.

Connect counter outputs A and C to the inputs of a 2-input AND gate, with its output connected to the Reset input.

- (b) **Complete** the 'C', 'B', 'A' columns in the table above, by adding a '0' or a '1', to show the counter outputs when pulse 3 has arrived. [1]

- (c) **Complete** the 'Red', 'Yellow' and 'Green' columns in the table above by adding either 'On' or 'Off' to show the state of each LED for each set of counter outputs. [3]

(4162-01)

Examiner only

| [1 | ] |

|----|---|

|    |   |

Examiner only **16.** A non-inverting amplifier has a voltage gain of 40. The upper graph shows the signal applied to its input. The lower graph shows the signal produced at its output. Voltage / mV 300 200 100 Time Input 0 -100 -200 -300 Voltage / V 9 6 3 ►Time Output 0 -3 -6 -9 Name the effect illustrated in the graphs. [1] (a) Which of the following could eliminate this problem? (b) (Tick  $(\checkmark)$  the correct answer.) [1] Reduce the voltage gain of the amplifier. Increase the voltage gain of the amplifier. Reduce the bandwidth of the amplifier. Increase the bandwidth of the amplifier.

Examiner only **17.** An inverting amplifier has a voltage gain of 40. The input signal has an **amplitude of 0.2V** and a **period of 1 ms**. Draw the wave on the graph below so that it shows the corresponding output signal. [2] Voltage/V 10 8 6 4 2 Time/ms 0 1.0 1.8 0.2 0.4 0.6 0.8 1.2 1.4 1.6 Ó -2 -4 -6 -8 -10 -

25

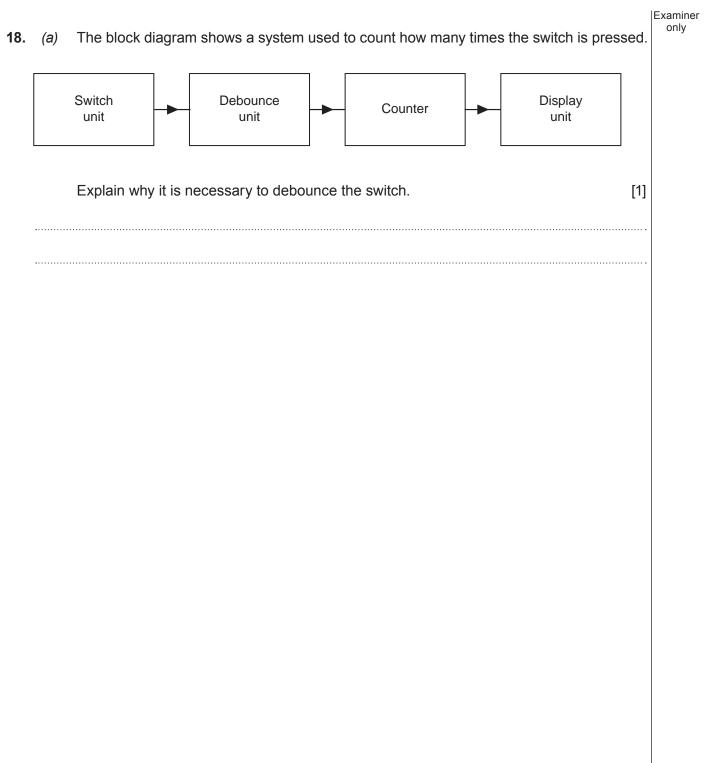

The debounce unit contains a Schmitt inverter. The performance of a Schmitt inverter is shown below. Voltage / V 4 3 2 Input 1 0 Time Voltage / V 6 5 4 Output 3 2 1 0 Time The input signal is shown in the top graph. The corresponding output signal is shown in the bottom graph. Complete the following sentences: The output of the Schmitt inverter changes from logic 1 to logic 0 when a rising (i) [1] input voltage reaches ...... V. The output of the Schmitt inverter changes from logic 0 to logic 1 when a falling (ii) input voltage reaches ..... V. [1]

(b)

Turn over.

Examiner only

|     |                                                                                | 28                                  |                           |        |  |  |

|-----|--------------------------------------------------------------------------------|-------------------------------------|---------------------------|--------|--|--|

| The | The circuit diagram for an interface and lamp unit is shown below.             |                                     |                           |        |  |  |

|     |                                                                                |                                     |                           |        |  |  |

|     | 12 V o-                                                                        |                                     | <b>—</b>                  |        |  |  |

|     |                                                                                | (                                   | lamp                      |        |  |  |

|     | sigi<br>fro<br>AND                                                             |                                     | )<br>]                    |        |  |  |

|     | 0 V o-                                                                         | I                                   | <b></b>                   |        |  |  |

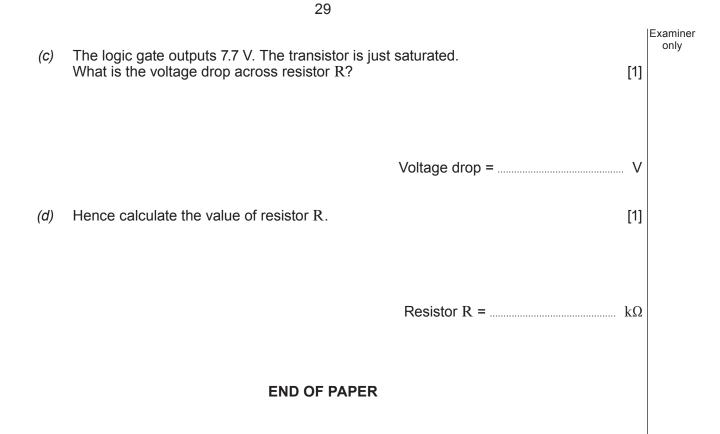

| (a) | The signal from the logic g                                                    |                                     | V (logic 0) to 7.7 V (log | ic 1). |  |  |

|     | <ul><li>(i) adding the correct vo</li></ul>                                    | oltages to the V <sub>1</sub> colun | nn.                       | [2]    |  |  |

|     |                                                                                | 'Off' to show the state             |                           | [2]    |  |  |

|     | (ii) Whang on or or or                                                         |                                     | or the lamp.              |        |  |  |

|     | Output of AND gate                                                             | V <sub>1</sub>                      | State of lamp             |        |  |  |

|     | 0.5V                                                                           | V                                   |                           |        |  |  |

|     | 7.7 V                                                                          | V                                   |                           |        |  |  |

| (b) | The bulb in the lamp unit is                                                   | s rated at 12 V, $100 \mathrm{mA}$  | ۸.                        |        |  |  |

|     | The transistor has a currer                                                    | nt gain ( $ m h_{FE}$ ) of 50.      |                           |        |  |  |

|     | Calculate the base current, $I_B$ , when the transistor is just saturated. [1] |                                     |                           |        |  |  |

|     |                                                                                |                                     |                           |        |  |  |

|     |                                                                                |                                     | Base current =            | mA     |  |  |

|     |                                                                                |                                     |                           |        |  |  |

|     |                                                                                |                                     |                           |        |  |  |

|     |                                                                                |                                     |                           |        |  |  |

19.

# **BLANK PAGE**

30

# **BLANK PAGE**

31