| Candidate Name | Centre Number | Candidate Number |

|----------------|---------------|------------------|

|                |               |                  |

## WELSH JOINT EDUCATION COMMITTEE

**General Certificate of Secondary Education**

#### CYD-BWYLLGOR ADDYSG CYMRU

Tystysgrif Gyffredinol Addysg Uwchradd

294/02

#### **ELECTRONICS**

#### **MODULE TEST E2**

#### HIGHER TIER

P.M. FRIDAY, 12 January 2007 (45 minutes)

For Examiner's use only

| Total<br>Mark |

|---------------|

|---------------|

#### ADDITIONAL MATERIALS

In addition to this examination paper you may need a calculator.

# INSTRUCTIONS TO CANDIDATES

Write your name, centre number and candidate number in the spaces at the top of this page.

Answer all the questions in the spaces provided in this booklet.

## INFORMATION FOR CANDIDATES

The number of marks is given in brackets at the end of each question or part-question.

No certificate will be awarded to a candidate detected in any unfair practice during the examination.

## Answer all questions.

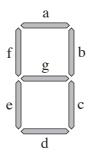

1. The diagram shows the arrangement of the LEDs in a seven-segment display.

Complete the following table, which shows the number/letter displayed when different segments are lit.

| Segment |   |   |   |   |   | Letter/Number<br>displayed |   |

|---------|---|---|---|---|---|----------------------------|---|

| a       | b | С | d | е | f | g                          |   |

| 1       | 0 |   |   |   |   |                            | F |

|         |   |   |   |   |   |                            | 3 |

| 0       | 1 | 1 | 0 | 1 | 1 | 1                          |   |

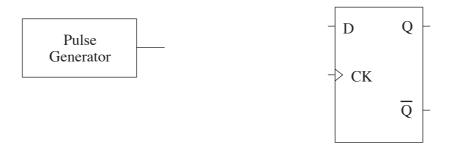

**2.** The diagram shows a pulse generator and a D-type flip-flop.

- (a) (i) The D-type must be connected so that it performs a *divide-by-two* action on pulses from the pulse generator.Draw the two connections needed to do this.

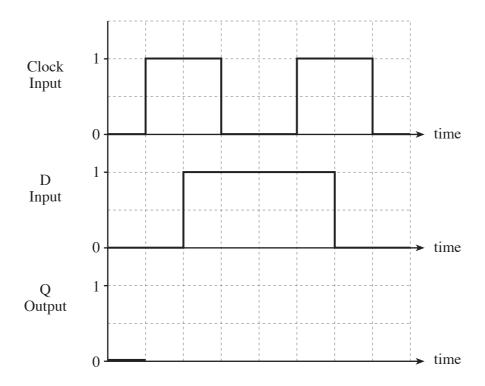

- (b) A D-type flip-flop can also be used for **data transfer**.

- (i) The D-type is *rising-edge* triggered. Label a rising-edge on the *Clock Input* graph.

(ii) The signal shown on the graph is applied to the D input.

Complete the graph to show the waveform obtained at the Q output.

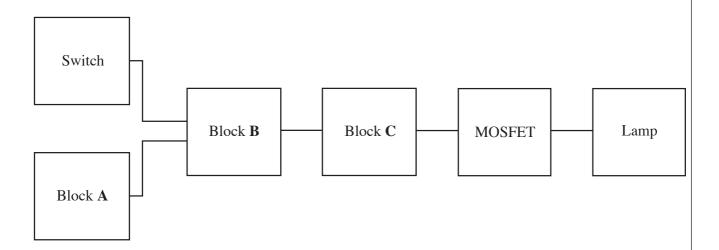

**3.** (a) Here is a system that controls a lamp on a stairway. The lamp comes on when the switch is pressed **but only** if it is dark. The lamp switches off automatically after 1 minute.

You can choose any of the following sub-systems to use for blocks A, B and C:-

Temperature sensing unit

Light sensing unit

OR gate

Delay unit

Pulse unit

AND gate

Which sub-system is

- (i) a suitable unit for block A?

- (ii) a suitable unit for block **B**?

- (b) Complete the circuit diagram to show how the MOSFET is connected to Block C and the lamp.

0V -

| (c) | The lighting control system is an example of electronics being used to conserve energy. |                                                                               |  |  |  |  |

|-----|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|--|--|--|--|

|     | (i)                                                                                     | Describe <b>another</b> example of electronics being used to conserve energy. |  |  |  |  |

|     |                                                                                         |                                                                               |  |  |  |  |

|     |                                                                                         |                                                                               |  |  |  |  |

|     | (ii)                                                                                    | Describe <b>one</b> benefit of electronics to a hospital patient.             |  |  |  |  |

|     |                                                                                         |                                                                               |  |  |  |  |

|     |                                                                                         | [2]                                                                           |  |  |  |  |

**4.** A logic system has two input sensors A and B, and three outputs P, Q and R. The truth table showing how the input sensors control the outputs is shown below.

| В | A | P | Q | R |

|---|---|---|---|---|

| 0 | 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 1 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 0 | 0 |

| (a)                                     | (i)   | Look at the P output. Which type of logic gate will provide this?                                                                                                   |     |

|-----------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|                                         |       | Logic gate is                                                                                                                                                       |     |

|                                         | (ii)  | Look at the Q output. Which type of logic gate will provide this?                                                                                                   |     |

|                                         |       | Logic gate is                                                                                                                                                       |     |

|                                         | (iii) | Look at the R output. It is the inverse of one of the inputs. Write down an expression to describe this output.                                                     |     |

|                                         |       | R =                                                                                                                                                                 |     |

|                                         |       |                                                                                                                                                                     | [3] |

| <i>(b)</i>                              |       | have a selection of AND, OR, NOT, NOR and NAND gates available. v a labelled diagram to show how the logic system can be made.                                      |     |

|                                         | A     | o—                                                                                                                                                                  |     |

|                                         |       |                                                                                                                                                                     |     |

|                                         |       | → Q                                                                                                                                                                 |     |

|                                         | п     |                                                                                                                                                                     |     |

|                                         | D     | o—                                                                                                                                                                  |     |

|                                         |       | → R                                                                                                                                                                 |     |

|                                         |       |                                                                                                                                                                     | [3] |

| (c)                                     | adva  | emory IC could be used to give the same output as the logic system. Give ntage, other than cost, of designing an electronic system using a memory IC instead gates. |     |

|                                         |       |                                                                                                                                                                     |     |

| • • • • • • • • • • • • • • • • • • • • |       |                                                                                                                                                                     |     |

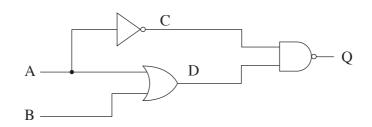

**5.** (a) Complete the truth table for the following logic system.

| В | A | С | D | Q |

|---|---|---|---|---|

| 0 | 0 |   |   |   |

| 0 | 1 |   |   |   |

| 1 | 0 |   |   |   |

| 1 | 1 |   |   |   |

[3]

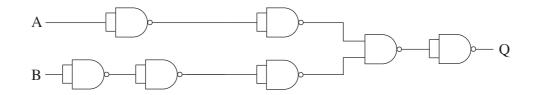

(b) Redraw the system to produce the same output, but using only NAND gates.

[2]

(c) Here is another system of NAND gates. Simplify it by crossing out any redundant gates.

[2]

(294-02)

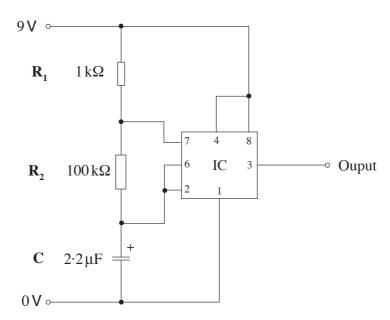

**6.** Here is the diagram for an astable circuit based on a 555 timer IC.

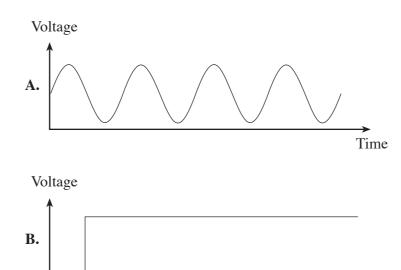

(a) Which of the following is the output waveform produced by an astable circuit?

Answer .....

Time

(b) The **approximate** value of frequency f of the pulse generator is given by the formula.

$f = \frac{\mathbf{0.7}}{\mathbf{R_2C}}$  (where f is in Hz, R<sub>2</sub> is in M $\Omega$  and C is in  $\mu$ F).

Use this formula to calculate the frequency of the pulse generator.

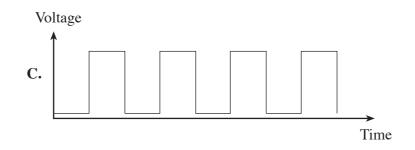

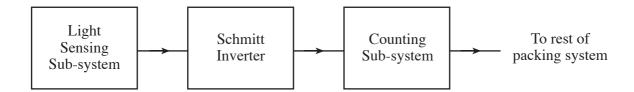

7. A company packs DVDs into boxes, five to a box.

Part of the packing system is shown in the following block diagram.

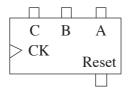

- The counting sub-system contains a 3-bit binary counter and an AND gate

- The system must reset when the **fifth** DVD passes the light sensor

- Taking the reset pin to logic 1 resets the counter

- Bit A of the counter is the least significant bit

- The counter is initially reset

- (a) Complete the diagram below to show how the AND gate is connected to the counter to allow it to reset correctly.

(b) The Schmitt inverter *cleans up* the signal produced by the light sensor. Here is part of a data sheet for a Schmitt Inverter:

When connected to 5 V supply:

- Logic 0 = 0 V

- Logic 1 = 5 V

- The output changes from logic 1 to logic 0 when a **rising** input voltage reaches 3 V

- The output changes from logic 0 to logic 1 when a **falling** input voltage reaches 1 V

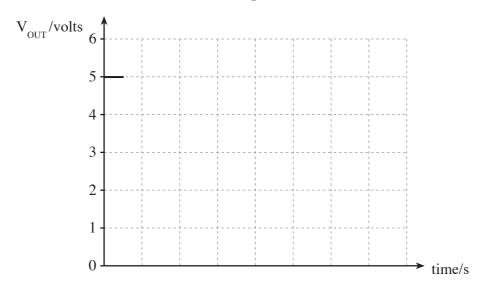

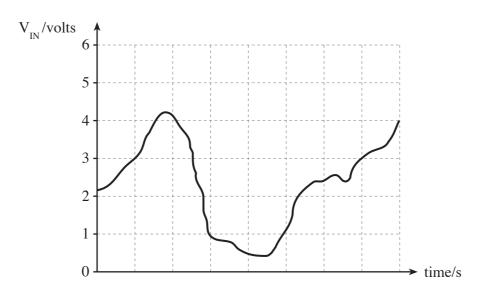

The signal produced by the light sensor is shown in **Graph 1**.

Complete Graph 2 to show the signal obtained at the output of the Schmitt Inverter.

Graph 1

Graph 2