## **General Certificate of Secondary Education**

# **Electronics 3432**

Tier F Foundation

# **Mark Scheme**

2008 examination – June series

Mark schemes are prepared by the Principal Examiner and considered, together with the relevant questions, by a panel of subject teachers. This mark scheme includes any amendments made at the standardisation meeting attended by all examiners and is the scheme which was used by them in this examination. The standardisation meeting ensures that the mark scheme covers the candidates' responses to questions and that every examiner understands and applies it in the same correct way. As preparation for the standardisation meeting each examiner analyses a number of candidates' scripts: alternative answers not already covered by the mark scheme are discussed at the meeting and legislated for. If, after this meeting, examiners encounter unusual answers which have not been discussed at the meeting they are required to refer these to the Principal Examiner.

It must be stressed that a mark scheme is a working document, in many cases further developed and expanded on the basis of candidates' reactions to a particular paper. Assumptions about future mark schemes on the basis of one year's document should be avoided; whilst the guiding principles of assessment remain constant, details will change, depending on the content of a particular examination paper.

Further copies of this Mark Scheme are available to download from the AQA Website: www.aqa.org.uk

Copyright © 2008 AQA and its licensors. All rights reserved.

#### COPYRIGHT

AQA retains the copyright on all its publications. However, registered centres for AQA are permitted to copy material from this booklet for their own internal use, with the following important exception: AQA cannot give permission to centres to photocopy any material that is acknowledged to a third party even for internal use within the centre.

Set and published by the Assessment and Qualifications Alliance.

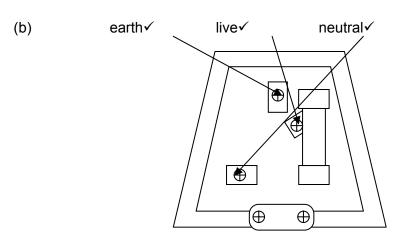

1 (a) blue ✓ green ✓ and yellow ✓ brown ✓

(c) earth pin ✓

fuse ✓

cable grip ✓ (any order)

Total - 10

**2** resistor symbol ✓ passive ✓

bipolar transistor symbol ✓ active ✓

diode symbol ✓ passive ✓

MOSFET symbol ✓ active ✓

capacitor symbol ✓ passive ✓

Total - 10

- **3** (a) (i) light sensor√

- (ii) lamp√

- (iii) comparator√

- (b) (i) comparator√

- (ii) light sensor√

- (iii) monostable√

- (c) comparator ✓ monostable ✓ MOSFET ✓ lamp ✓ time ✓

OR light sensor ✓ comparator ✓ monostable ✓ driver ✓ (4 max, -1 per error)

**4** (a) (i) two inputs labelled A and B✓ OR gate symbol✓ output labelled Q✓

(ii)

| А | В | Q  |

|---|---|----|

| 0 | 0 | 0✓ |

| 0 | 1 | 1√ |

| 1 | 0 | 1√ |

| 1 | 1 | 1√ |

- (b) (i) AND gate ✓

- (ii) high√ high√

Total - 10

- 5 (a) (i) transistor, or MOSFET, or (three terminal) regulator IC✓ switching or regulating as appropriate to above✓

- (ii) Collector ✓ Base ✓ Emitter ✓, or Drain ✓ Gate ✓ Source ✓, or i/p ✓ com ✓ o/p ✓ as appropriate to above ✓

- (b) (i) resistor√ limits current√

- (ii) 22√

- (iii) 3W√

- (iv) 5%✓

- **6** (a) (i) af amplifier ✓

- (ii) demodulator√

- (iii) tuned circuit√

- (iv) loudspeaker√

- (v) aerial√

- (b) integrated circuit√

- (c) (i) increases√

- (ii) stays the same√

- (iii) increases√

- (iv) increases√

Total - 10

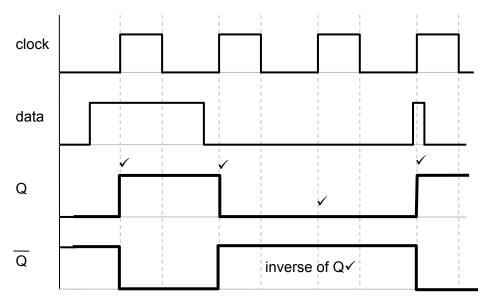

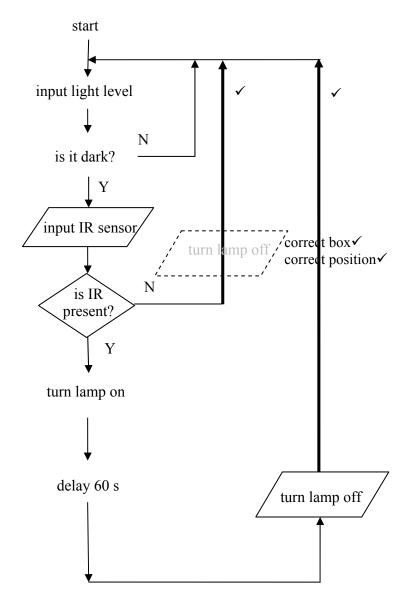

### **7** (a)

- (b) (i) resistor√

- (ii) 3.8V✓

- (iii) 380Ω√

- (iv) 390Ω√

- (v) 38mW√

start

input light

sensor

is it dark?

turn on lamp

delay 60s

a loop is any line that returns to a point earlier in the flow chart  $\checkmark$

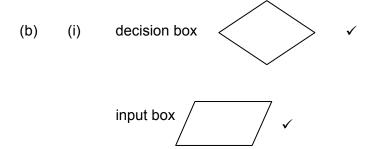

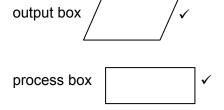

(b) (ii) & (iii)

- (c) light level is inputted, is dark detected? ✓ if yes, is IR detected? ✓ if yes turn on lamp ✓ wait 60s before repeat ✓

- (d) (i) turn off lamp occurs after 60s delay, then switches on again√

- (ii) "turn off lamp" ✓

- (iii) on diagram above

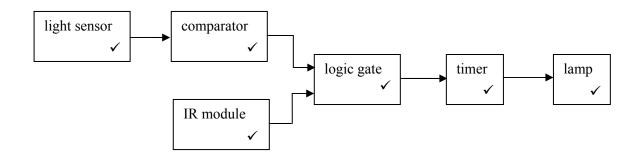

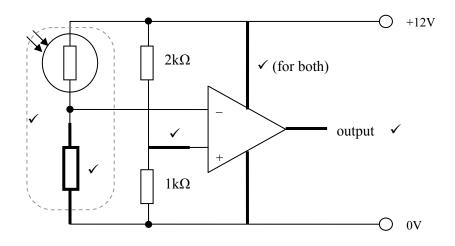

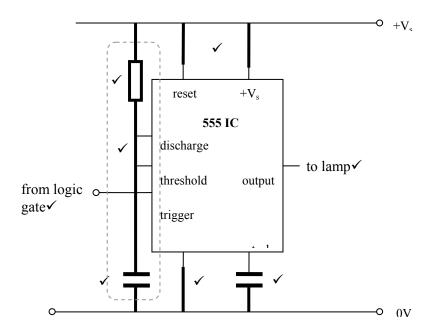

## **9** (a)

## (b) (i) & (iii)

- (ii) 4V√

- (iv) 100kΩ√

- (c) (i)

| light sensor | IR module | output |

|--------------|-----------|--------|

| 0            | 0         | 1√     |

| 0            | 1         | 1√     |

| 1            | 0         | 1√     |

| 1            | 1         | 0 ✓    |

(ii) NAND✓

(d) (i) & (ii) 1 mark for each correct component in ring✓✓

- (e) (i) relay√

- (ii) diode√

Total - 30

Paper Total – 120