Surname

Centre

2

Candidate Number

Other Names

**GCE AS/A level**

1141/01

# **ELECTRONICS – ET1**

P.M. MONDAY, 12 May 2014

1 hour 15 minutes

| For Examiner's use only |                 |                 |  |

|-------------------------|-----------------|-----------------|--|

| Question                | Maximum<br>Mark | Mark<br>Awarded |  |

| 1.                      | 8               |                 |  |

| 2.                      | 6               |                 |  |

| 3.                      | 9               |                 |  |

| 4.                      | 7               |                 |  |

| 5.                      | 6               |                 |  |

| 6.                      | 5               |                 |  |

| 7.                      | 7               |                 |  |

| 8.                      | 12              |                 |  |

| Total                   | 60              |                 |  |

## **ADDITIONAL MATERIALS**

In addition to this examination paper, you will need a calculator.

## INSTRUCTIONS TO CANDIDATES

Use black ink or black ball-point pen.

Write your name, centre number and candidate number in the spaces at the top of this page. Answer all questions.

Write your answers in the spaces provided in this booklet.

## INFORMATION FOR CANDIDATES

The total number of marks available for this paper is 60.

The number of marks is given in brackets at the end of each question or part-question.

You are reminded of the necessity for good English and orderly presentation in your answers.

You are reminded to show all working. Credit is given for correct working even when the final answer given is incorrect.

#### **INFORMATION FOR THE USE OF CANDIDATES IN ET1**

#### **Preferred Values for resistors**

The figures shown below and their decade multiples and sub-multiples are the E24 series of preferred values.

10, 11, 12, 13, 15, 16, 18, 20, 22, 24, 27, 30, 33, 36, 39, 43, 47, 51, 56, 62, 68, 75, 82, 91.

# **Standard Multipliers**

| Prefix | Multiplier       |

|--------|------------------|

| Т      | $\times 10^{12}$ |

| G      | $\times 10^9$    |

| М      | $\times 10^{6}$  |

| k      | $\times 10^3$    |

| Prefix | Multiplier        |

|--------|-------------------|

| m      | $	imes 10^{-3}$   |

| μ      | $	imes 10^{-6}$   |

| n      | $\times 10^{-9}$  |

| р      | $\times 10^{-12}$ |

**Operational amplifier**

$$G = -\frac{R_F}{R_{IN}}$$

$$=-\frac{R_{\rm F}}{R_{\rm P}}$$

$$G = 1 + \frac{R_F}{R_1}$$

Slew Rate =

$$\frac{\Delta V_{OUT}}{\Delta t}$$

**Boolean identities**

$$A + \overline{A} \cdot B = A + B$$

$$A.B + A = A.(B+1) = A$$

# **BLANK PAGE**

3

Turn over.

1141 010003

|Examiner The following diagram shows a logic system. 1.  $Q_1$ A ° --- Q<sub>3</sub>  $Q_2$ Logic Gate **B** ∽ The partially completed truth table for the logic system is shown below. (a) **INPUTS OUTPUTS** B  $\mathbf{Q}_2$  $Q_3$ Α  $Q_1$ 0 0 0 0 1 1 1 1 0 1 1 0 Identify the logic gate that gives output  $\boldsymbol{Q}_2.$ (i) [1] Gate Complete the truth table for the outputs  $Q_1$  and  $Q_3$ . (ii) [2] Give the Boolean expression for each of the outputs  $Q_1,\,Q_2\,\mbox{and}\,\,Q_3$  in terms of A and B(b) [3] Q<sub>1</sub> = ...... Q<sub>2</sub> = ...... Q<sub>3 =</sub> Name the single gate that would produce the same output as  $Q_3$ . (C) [1]

4

only

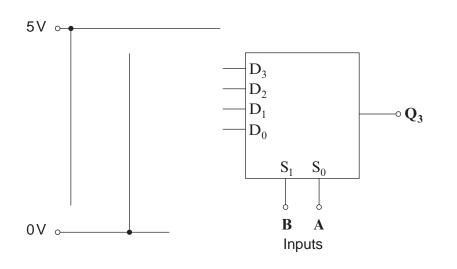

(d) Show on the following diagram how the same output  $Q_3$  could be generated using a multiplexer. [1]

5

Examiner

(1141-01)

Examiner only

**2.** The truth table for a logic gate is given below.

| В | Α | Q |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 0 |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

(a) Using only AND, OR and NOT gates, draw a diagram of a logic system that will produce this truth table. [1]

(b) Redraw your system in part (a) using only NAND gates.

(c) Draw lines through all redundant gates.

[2]

[3]

|Examiner only 3. Simplify the following expressions, showing your working where appropriate. (a) Ā.1 = ..... (i) [1]  $(B + \bar{A}).(\bar{B} + A) =$ (ii) [2] A different logic system produced the Karnaugh map shown below. (b) BA 00 01 11 10 DC 0 0 1 1 00 01 1 1 0 0 11 1 1 0 1 10 0 0 1 1 1141 010007 Give the simplest Boolean expression for the output Q of this logic system. Show any groups that you create on the map. [3] Apply DeMorgan's theorem to the following expression and simplify the result. (C) All steps of the simplification must be shown. [3]  $Q = (\overline{\overline{A}.\overline{B}}).(A + \overline{\overline{B}})$

7

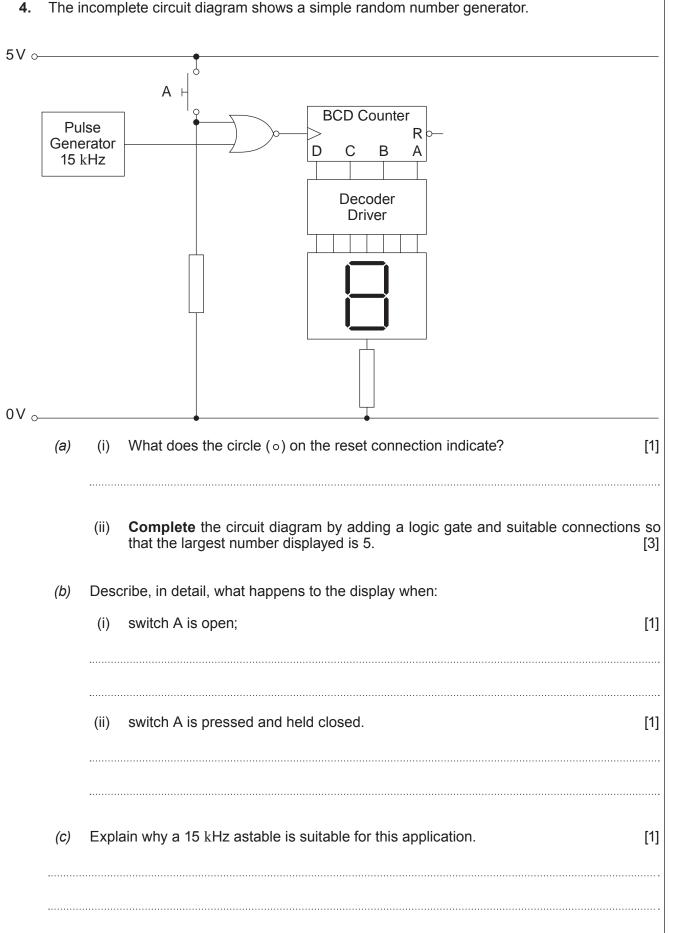

The incomplete circuit diagram shows a simple random number generator.

8

Examiner only

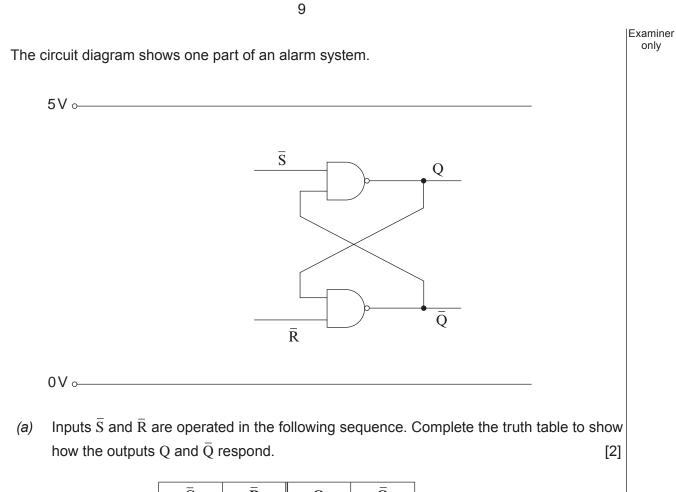

5.

| $\bar{\mathbf{S}}$ | R | Q | Q |

|--------------------|---|---|---|

| 1                  | 1 | 0 |   |

| 0                  | 1 |   |   |

| 1                  | 1 |   |   |

| 1                  | 0 |   |   |

| 1                  | 1 |   |   |

- (b) Add the necessary components to the diagram such that the  $\overline{S}$  input can be used to **set** Q to logic 1 when a switch is momentarily pressed. [2]

- (c) The output of the alarm is a LED. Complete the diagram to show how the LED can be used to indicate the logic state of  $\overline{Q}$ . The LED should be ON when  $\overline{Q}$  is **sinking a current**. [2]

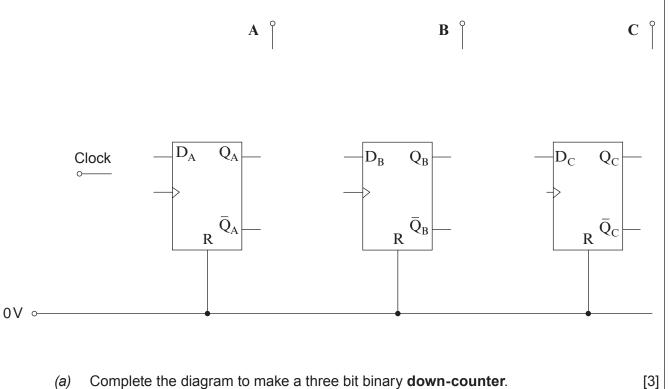

The diagram shows 3 D-type flip-flops, which form part of a binary **down-counter**. 6. Outputs A, B and C are used to indicate the binary output. A is the least significant bit.

The initial state of the counter is shown in the table. Complete the table, using **0** or **1**, to (b) indicate the logic state of each output after the stated number of clock pulses. [2]

|                           | OUTPUT<br>C | OUTPUT<br>B | OUTPUT<br>A |

|---------------------------|-------------|-------------|-------------|

| Initial State             | 1           | 1           | 1           |

| After ONE<br>clock pulse  |             |             |             |

| After SIX<br>clock pulses |             |             |             |

(a)

Examiner only

[3]

# **BLANK PAGE**

11

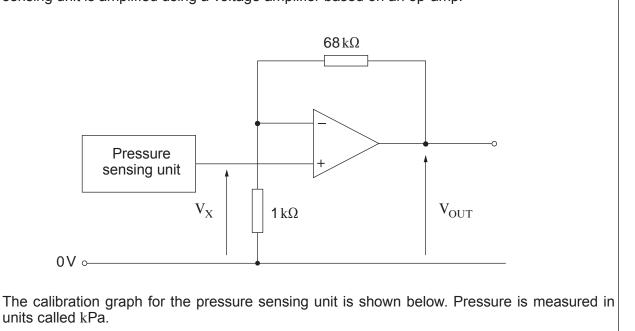

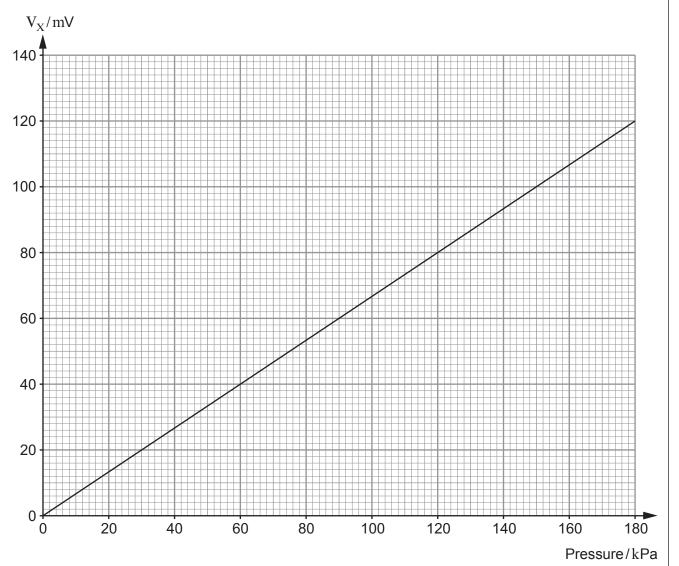

7. The circuit diagram shows part of a diver's pressure gauge system. The output of the pressure sensing unit is amplified using a voltage amplifier based on an op-amp.

© WJEC CBAC Ltd.

Examiner only

| (a) | What is the voltage gain of the amplifier? [1]                                                           | Examiner<br>only |

|-----|----------------------------------------------------------------------------------------------------------|------------------|

|     |                                                                                                          |                  |

| (b) | Use the calibration graph to:<br>(i) determine the pressure when $V_X$ = 90 mV;                          |                  |

|     | (ii) calculate the output voltage $V_{OUT}$ of the amplifier at 110 kPa. [3]                             |                  |

| (c) | The op-amp saturates at $\pm$ 8.0 V. Determine the <b>maximum</b> pressure that this system can measure. |                  |

|     |                                                                                                          |                  |

13

Turn over.

8. A data sheet for an op-amp is given below.

| Parameter                              | Value                    |

|----------------------------------------|--------------------------|

| Open-loop gain                         | 3.0 x 10 <sup>5</sup>    |

| Input impedance                        | 2.0 x 10 <sup>12</sup> Ω |

| Saturation voltage for a ± 13 V supply | ±12V                     |

| Slew rate                              | 4.8 V μs <sup>-1</sup>   |

| Gain-bandwidth product                 | 3.6 MHz                  |

The op-amp is powered from a  $\pm$  13 V supply.

An amplifier has a **variable** voltage gain. The minimum voltage gain is 0 and the maximum voltage gain is -60.

(a) Complete the circuit diagram for a voltage amplifier with this specification.

[3]

Input o-----

0 V o------

15

| (b) | (i)          | Calculate the <b>two</b> resistance values which give a maximum voltage gain of –60.<br>Identify the feedback resistance. [2]            |  |

|-----|--------------|------------------------------------------------------------------------------------------------------------------------------------------|--|

|     | (ii)         | What is the input impedance of this voltage amplifier? [1]                                                                               |  |

| (C) | The<br>volta | e voltage gain is adjusted and the output voltage measured to be $-9V$ when the input age is 200 mV. Calculate the new voltage gain. [1] |  |

| (d) |              | e voltage gain is changed to –30. Calculate the maximum bandwidth of the amplifier<br>in this voltage gain. [2]                          |  |

|     |              | TURN OVER FOR THE<br>REST OF THE QUESTION.                                                                                               |  |

Turn over.

only (e) The following signal is applied to the input to illustrate the effect of slew-rate on the output of the voltage amplifier. Draw the output voltage on the axes below.  $V_{OUT} \mbox{ is initially at 0V}.$ [3]  $V_{\rm IN}$  / V 10 5 0, 0 2 4 6 8 10 12 14 Time /  $\mu$ s  $V_{OUT}$  / V 15-10 5 0 10 14 8 12 6 Time / µs -5 -10 -15

**END OF PAPER**

Examiner