## **GCE MARKING SCHEME**

## **SUMMER 2016**

ELECTRONICS ET5 1145/01

© WJEC CBAC Ltd.

## INTRODUCTION

This marking scheme was used by WJEC for the 2016 examination. It was finalised after detailed discussion at examiners' conferences by all the examiners involved in the assessment. The conference was held shortly after the paper was taken so that reference could be made to the full range of candidates' responses, with photocopied scripts forming the basis of discussion. The aim of the conference was to ensure that the marking scheme was interpreted and applied in the same way by all examiners.

It is hoped that this information will be of assistance to centres but it is recognised at the same time that, without the benefit of participation in the examiners' conference, teachers may have different views on certain matters of detail or interpretation.

WJEC regrets that it cannot enter into any discussion or correspondence about this marking scheme.

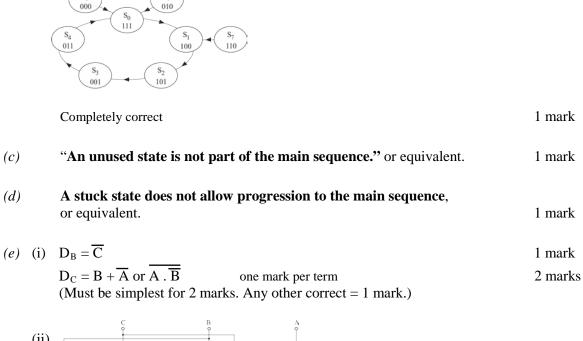

**1.** (*a*)

|       | Cur | <b>Current Outputs</b> |   |    | Next Outputs |    |  |

|-------|-----|------------------------|---|----|--------------|----|--|

| State | С   | В                      | Α | Dc | DB           | DA |  |

| 0     | 1   | 1                      | 1 | 1  | 0            | 0  |  |

| 1     | 1   | 0                      | 0 | 1  | 0            | 1  |  |

| 2     | 1   | 0                      | 1 | 0  | 0            | 1  |  |

| 3     | 0   | 0                      | 1 | 0  | 1            | 1  |  |

| 4     | 0   | 1                      | 1 | 1  | 1            | 1  |  |

| 5     | 0   | 0                      | 0 | 1  | 1            | 1  |  |

| 6     | 0   | 1                      | 0 | 1  | 1            | 1  |  |

| 7     | 1   | 1                      | 0 | 1  | 0            | 0  |  |

Five correct 'current' states identified 1 mark Correct progression into 'Next Output' 1 mark States in correct order in table 1 mark ('Next Outputs =  $0\ 0\ 0$ ' for state 4 = 1 mark total.)

(b)

(*c*)

*(d)*

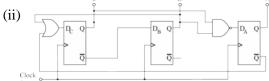

Allow ecf from (e) for  $D_B$  and  $D_C$ 1 mark Clock connections correct 1 mark D<sub>C</sub> correct 1 mark D<sub>B</sub> correct D<sub>A</sub> correct 1 mark Use of  $\overline{Q}$ 1 mark (Allow ecf from (e) for  $D_B$  and  $D_C$ )

Total for Q1

14

| 2. | (a)            |                                                                                                                                                                                                                                                                                         |         |

|----|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|    |                | 0V                                                                                                                                                                                                                                                                                      |         |

|    |                | Capacitor in series with resistor                                                                                                                                                                                                                                                       | 1 mark  |

|    |                | RC network in input circuit                                                                                                                                                                                                                                                             | 1 mark  |

|    |                | Remainder of circuit correct                                                                                                                                                                                                                                                            | 1 mark  |

|    | <i>(b)</i>     | (i) Correct multipliers in break frequency formula                                                                                                                                                                                                                                      | 1 mark  |

|    |                | Break frequency = $995 \text{ Hz}$ (accept $994.7 \text{ Hz}$ ).                                                                                                                                                                                                                        | 1 mark  |

|    |                | (ii) Low frequency voltage gain = 12 (or -12)                                                                                                                                                                                                                                           | 1 mark  |

|    | (c)            | (i) Filter = treble boost                                                                                                                                                                                                                                                               | 1 mark  |

|    | (0)            | <ul><li>(ii) Break frequency = 3 kHz</li></ul>                                                                                                                                                                                                                                          | 1 mark  |

|    |                | Total for Q2                                                                                                                                                                                                                                                                            | 8       |

|    |                |                                                                                                                                                                                                                                                                                         | o       |

| 3. | ( <i>a</i> )   | (i) Voltage at $X = 0.1 V$                                                                                                                                                                                                                                                              | 1 mark  |

|    | ()             | (ii) Binary output = $10$                                                                                                                                                                                                                                                               | 1 mark  |

|    |                | (iii) Smallest $V_{IN} = 0.4 V$ (accept ">0.4 V")                                                                                                                                                                                                                                       | 1 mark  |

|    | (b)            | (i) Resolution = $0.0625 \text{ V} (=1/16 \text{ V}) (\text{accept } 0.063 \text{ V})$                                                                                                                                                                                                  | 1 mark  |

|    | ( )            | (ii) $V_{\text{REF}} = 1.0 \text{ V}$                                                                                                                                                                                                                                                   | 1 mark  |

|    |                | (iii) No. of resistors $= 16$                                                                                                                                                                                                                                                           | 1 mark  |

|    |                | Total for Q3                                                                                                                                                                                                                                                                            | 6       |

| 4. | (a)            | Answer = $D(00011)$                                                                                                                                                                                                                                                                     | 1 mark  |

|    | $(\mathbf{b})$ | movlw $b'10010XXX'$ (X = don't care)                                                                                                                                                                                                                                                    |         |

|    | (b)            | Enable GIE (set bit 7) $(X - doint care)$                                                                                                                                                                                                                                               | 1 mark  |

|    |                | Enable INTE and disable all others (set bit 4, reset bits 6, 5, 3)                                                                                                                                                                                                                      | 1 mark  |

|    |                | (Answer must be 8 bits)                                                                                                                                                                                                                                                                 |         |

|    | (c)            | 220 alarmmovwfprotect; store contents of W in register called 'protect';221bsfPORTA, 2; output logic 1 to switch on buzzer;222calltensec; call ten second delay subroutine;223btfssPORTA,0; test reset switch - ignore next instruction if pressed;224gotoalarm; jump back to line 220; | - 1     |

|    |                | One mark per correct line<br>( Lower case used in 'PORTA' or upper case in 'alarm' loses 1 mark)                                                                                                                                                                                        | 5 marks |

|    |                | (Lower case used in TORTA of upper case in alarm loses I mark)                                                                                                                                                                                                                          |         |

|    |                | Total for O4                                                                                                                                                                                                                                                                            | 8       |

Total for Q4

8

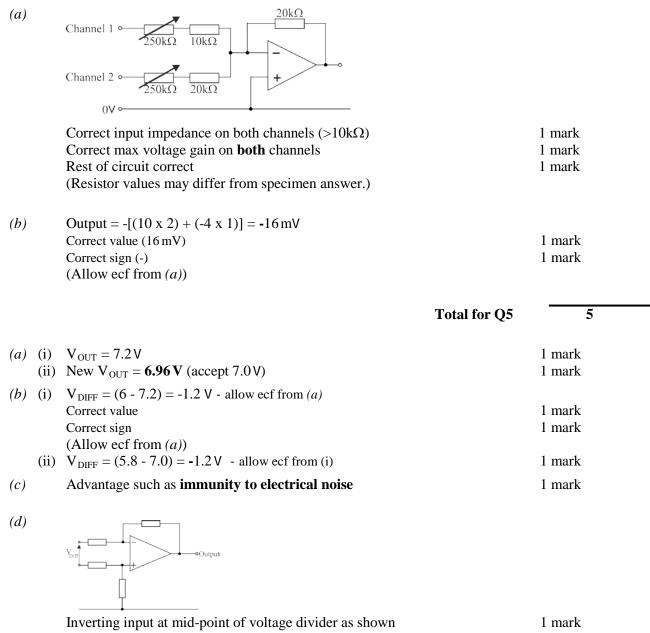

**5.** (*a*)

6.

|                                                              | Total for Of |   | 0    |  |

|--------------------------------------------------------------|--------------|---|------|--|

| Correct ratio to give voltage gain of 100                    |              | 1 | mark |  |

| Non-inverting input at mid-point of voltage divider as shown |              | 1 | mark |  |

| Inverting input at mid-point of voltage divider as shown     |              | 1 | mark |  |

Total for Q6

9

| 7. | (a)          |                      | +4SV<br>Heater<br>A<br>B<br>OV                                                                                                                                                                                                                                                                                                                                                                                   |                                                             |

|----|--------------|----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|

|    |              | (i)<br>(ii)          | Correct connection for switch, labelled A and resistor<br>Correct connection for switch, labelled B<br>Resistor in series with switch<br>Correct connection for capacitor                                                                                                                                                                                                                                        | 1 mark<br>1 mark<br>1 mark<br>1 mark                        |

|    | (b)          | (i)<br>(ii)          | Voltage at $X = 0V$<br>Voltage above switch B drops from $48V$ to $0V$ when switch is pressed<br>so voltage at X drops by $48V$ to $-48V$<br>thyristor is momentarily reverse biased and switches off, or equivalent                                                                                                                                                                                             | 1 mark<br>1 mark<br>1 mark<br>1 mark                        |

|    | (c)          |                      | Advantage such as no moving parts so no wear from friction<br>Total for Q7                                                                                                                                                                                                                                                                                                                                       | 1 <u>mark</u><br>9                                          |

| 8. | (a)          |                      | Link <b>S</b><br>(Other links included - zero marks)                                                                                                                                                                                                                                                                                                                                                             | 1 mark                                                      |

|    | (b)          |                      | $R_1 = R_2$                                                                                                                                                                                                                                                                                                                                                                                                      | 1 mark                                                      |

|    | ( <i>c</i> ) | (i)<br>(ii)<br>(iii) | $V_{OUT} = 2.3 V$<br>Power dissipation = 0.66 W (accept 0.7 W)                                                                                                                                                                                                                                                                                                                                                   | 1 mark                                                      |

|    |              |                      | 2.3 2<br>0 + + + Time<br>-246 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 +6 + |                                                             |

|    |              |                      | Signal centred on +2.3 V                                                                                                                                                                                                                                                                                                                                                                                         | 1 mark                                                      |

|    |              |                      | Sinusoidal signal of amplitude 2 V                                                                                                                                                                                                                                                                                                                                                                               | 1 mark                                                      |

|    | ( <i>d</i> ) | (i)                  |                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                             |

|    |              |                      | Use of complementary pair<br>Common emitter connection to output<br>Common base connection to input<br>Max. power dissipation = 18 W<br>Advantage such as zero quiescent power dissipation<br><b>Total for Q8</b>                                                                                                                                                                                                | 1 mark<br>1 mark<br>1 mark<br>1 mark<br>1 mark<br><b>11</b> |

GCE Electronics ET5 MS Summer 2016/CJ