| Centre Number       |  |  | Candidate Number |  |  |

|---------------------|--|--|------------------|--|--|

| Surname             |  |  |                  |  |  |

| Other Names         |  |  |                  |  |  |

| Candidate Signature |  |  |                  |  |  |

| A | Q | A        |  |

|---|---|----------|--|

|   |   | <i> </i> |  |

General Certificate of Education Advanced Subsidiary Examination June 2015

## **Electronics**

ELEC2

## Unit 2 Further Electronics

Thursday 21 May 2015 1.30 pm to 2.30 pm

### For this paper you must have:

- a pencil and ruler

- a calculator

- a Data Sheet (enclosed).

#### Time allowed

• 1 hour

### Instructions

- Use black ink or black ball-point pen.

- Fill in the boxes at the top of this page.

- Answer all questions.

- You must answer the questions in the spaces provided. Do not write outside the box around each page or on blank pages.

- Do all rough work in this book. Cross through any work you do not want to be marked.

#### Information

- The marks for questions are shown in brackets.

- The maximum mark for this paper is 67.

## Answer all questions in the spaces provided.

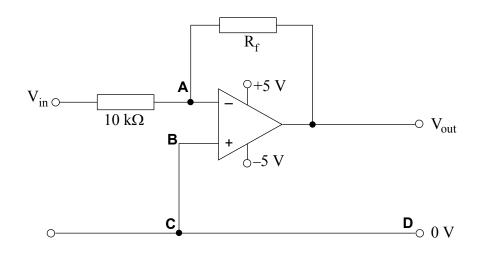

**1 Figure 1** shows an inverting op-amp amplifier subsystem.

Figure 1

| 1 (a) (i) | Write in the box the letter that corresponds to the virtual earth point in <b>Figur</b> | e 1. |       |

|-----------|-----------------------------------------------------------------------------------------|------|-------|

|           |                                                                                         | [1   | mark] |

| 1 (a) (ii) | Explain the meaning of the term <b>virtual earth point</b> . | [2 marks] |

|------------|--------------------------------------------------------------|-----------|

|            |                                                              |           |

|            |                                                              |           |

| 1 (a) (iii) | State the input resistance of this amplifier subsystem. |          |

|-------------|---------------------------------------------------------|----------|

|             |                                                         | [1 mark] |

| 1 (b) | Calculate the value of $R_f$ needed to give the amplifier subsystem a voltage gain of $-47$ . |

|-------|-----------------------------------------------------------------------------------------------|

|       | [3 marks]                                                                                     |

|       |                                                                                               |

|       |                                                                                               |

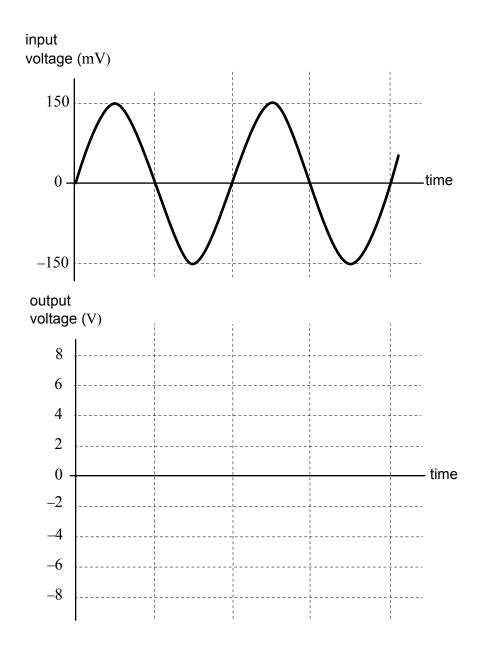

1 (c) The amplifier subsystem in part (b) is used to increase the signal voltage from an electric guitar.

The voltage from the guitar to the amplifier input is shown in Figure 2.

Draw onto the lower part of **Figure 2** the output signal from the amplifier subsystem. **[4 marks]**

Figure 2

11

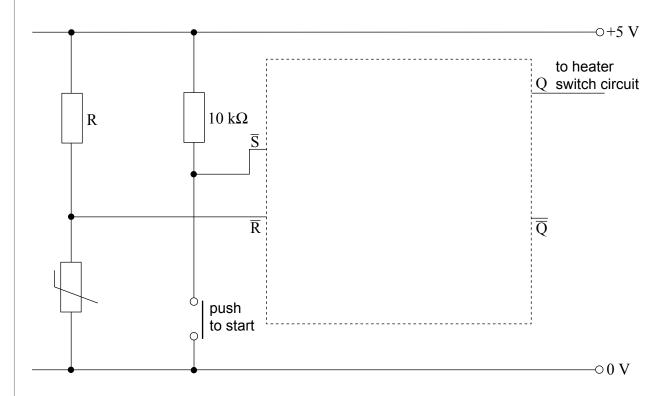

An electric heater is used to heat water to 50 °C in a storage tank. The owner switches on the heater to warm the water but sometimes forgets to turn the heater off once the water is hot enough, so wasting energy.

**Figure 3** shows a partially completed circuit diagram of a system to automatically switch off the heater when the temperature has reached  $50 \, ^{\circ}\text{C}$ .

Figure 3

**2 (a)** Complete the circuit diagram in **Figure 3** by drawing a NAND gate bistable inside the dashed box.

[4 marks]

**2 (b)** When the water temperature is greater than 50 °C the input  $\overline{R}$  is low.

Complete **Table 1** for the operation of the system. The first row has been completed for you.

[4 marks]

Table 1

| Push switch state | Water temperature | Q | $\overline{\mathbf{Q}}$ |

|-------------------|-------------------|---|-------------------------|

| open              | <50 °C            | 0 | 1                       |

| closed            | <50 °C            |   |                         |

| open              | >50 °C            |   |                         |

| closed            | >50 °C            |   |                         |

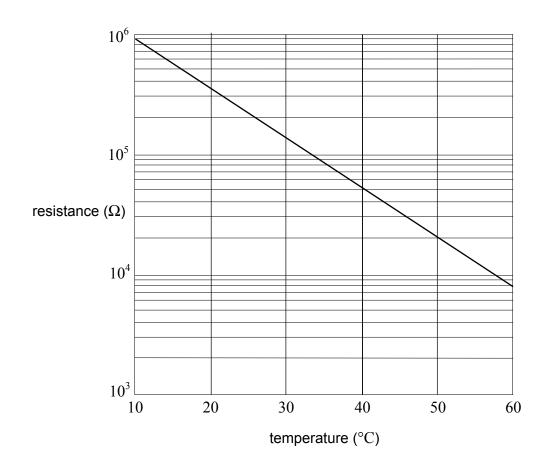

2 (c) A thermistor is used to sense the water temperature. Figure 4 shows the characteristic of the thermistor.

Figure 4

For the NAND gates used, an input voltage of less than  $2.5~\rm V$  is logic 0, an input voltage of greater than or equal to  $2.5~\rm V$  is logic 1.

Determine a suitable value for R so that the circuit will switch off the heater when the temperature reaches  $50\ ^{\circ}C.$

Show how you arrived at your value.

| [3 ma | ırksj |

|-------|-------|

|       |       |

|       |       |

|       |       |

|       |       |

|       |       |

|       |       |

|       |       |

|       |       |

- A student builds a push-pull audio amplifier for his coursework project.

After completing the amplifier, he tests it and is disappointed with the output sound at low and high volume settings.

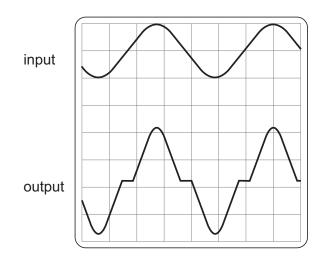

- **3 (a)** The oscilloscope trace in **Figure 5** shows the input and output signals at a low volume setting.

Figure 5

| [1 mark]  | State the name of this type of distortion.   | 3 (a) (i)   |

|-----------|----------------------------------------------|-------------|

| [3 marks] | Explain what causes this type of distortion. | 3 (a) (ii)  |

|           |                                              |             |

|           |                                              |             |

| [1 mark]  | State how this distortion can be reduced.    | 3 (a) (iii) |

|           |                                              |             |

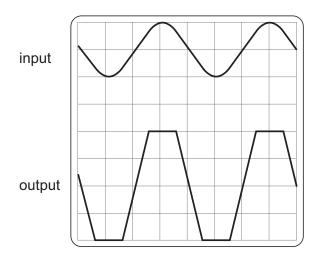

3 (b) The oscilloscope trace in **Figure 6** shows the input and output signals at a high volume setting when the amplifier is connected to an  $8\ \Omega$  loudspeaker.

Figure 6

| 3 | (b) (i)   | State the name of this type of distortion.   | [1 mark]  |

|---|-----------|----------------------------------------------|-----------|

| 3 | (b) (ii)  | Explain what causes this type of distortion. | [2 marks] |

|   |           |                                              |           |

| 3 | (b) (iii) | State how this distortion can be reduced.    | [1 mark]  |

|   |           |                                              |           |

Question 3 continues on the next page

| 3 (c) | The y-sensitivity for the output trace in <b>Figure 6</b> is $10~V/div$ . Estimate, using a calculation, the maximum undistorted output power of the amplifier into an $8~\Omega$ loudspeaker, assuming the distortion in part (a) is made negligible. [3 marks] |  |  |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|       |                                                                                                                                                                                                                                                                  |  |  |  |  |

|       |                                                                                                                                                                                                                                                                  |  |  |  |  |

|       |                                                                                                                                                                                                                                                                  |  |  |  |  |

|       |                                                                                                                                                                                                                                                                  |  |  |  |  |

|       |                                                                                                                                                                                                                                                                  |  |  |  |  |

|       |                                                                                                                                                                                                                                                                  |  |  |  |  |

|       |                                                                                                                                                                                                                                                                  |  |  |  |  |

|       |                                                                                                                                                                                                                                                                  |  |  |  |  |

|       |                                                                                                                                                                                                                                                                  |  |  |  |  |

|       |                                                                                                                                                                                                                                                                  |  |  |  |  |

|       |                                                                                                                                                                                                                                                                  |  |  |  |  |

|       |                                                                                                                                                                                                                                                                  |  |  |  |  |

|       |                                                                                                                                                                                                                                                                  |  |  |  |  |

|       |                                                                                                                                                                                                                                                                  |  |  |  |  |

|       |                                                                                                                                                                                                                                                                  |  |  |  |  |

|       |                                                                                                                                                                                                                                                                  |  |  |  |  |

|       |                                                                                                                                                                                                                                                                  |  |  |  |  |

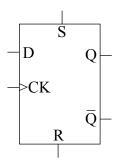

**Figure 7** shows the symbol for a rising edge triggered D-type flip-flop.

Figure 7

| 4 (a) | Explain what is meant by the term rising edge triggered |

|-------|---------------------------------------------------------|

|       | You should refer to CK, D and Q in your answer.         |

| [2 mark | S     |

|---------|-------|

|         |       |

|         | • • • |

|         |       |

| 4 (b) | Draw, in the space below, the circuit diagram of a ÷2 frequency divider (counter) which |

|-------|-----------------------------------------------------------------------------------------|

|       | uses a D-type flip-flop.                                                                |

|       | Label the input and output.                                                             |

[3 marks]

4 (c) The circuit in Figure 8 uses two rising edge triggered D-type flip-flops.

Figure 8

Complete **Table 2** for the operation of this system. The first four rows have been completed for you.

[4 marks]

Table 2

| Clock<br>pulse<br>number | Clock | D <sub>1</sub> | Q <sub>1</sub> | $\overline{\mathbf{Q}}_{1}$ | D <sub>2</sub> | $Q_2$ | $\overline{\mathrm{Q}}_2$ |

|--------------------------|-------|----------------|----------------|-----------------------------|----------------|-------|---------------------------|

| 0                        |       | 0              | 0              | 1                           | 1              | 0     | 1                         |

| 1                        | 1     | 1              | 0              | 1                           | 1              | 1     | 0                         |

| 2                        | 1     | 1              | 1              | 0                           | 0              | 1     | 0                         |

| 3                        | 1     | 0              | 1              | 0                           | 0              | 0     | 1                         |

| 4                        | 1     |                |                |                             |                |       |                           |

| 5                        | 1     |                |                |                             |                |       |                           |

| 6                        | 1     |                |                |                             |                |       |                           |

| 7                        | 1     |                |                |                             |                |       |                           |

| 4 (d) (i)  | State the ratio of the frequency of the clock pulses to the pulses at $\boldsymbol{Q}_1.$     | [1 mark] |

|------------|-----------------------------------------------------------------------------------------------|----------|

| 4 (d) (ii) | State the timing difference between the signals at $\boldsymbol{Q}_1$ and $\boldsymbol{Q}_2.$ | [1 mark] |

|            |                                                                                               |          |

Turn over ▶

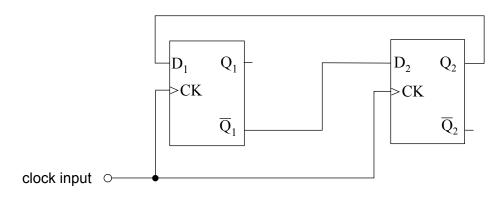

A student uses a variable voltage power supply to control the speed of a 12 V drill for drilling printed circuit boards. The student finds that the drill stalls easily at low speed. Researching on the Internet, he finds that speed controllers for drills usually supply 12 V pulses to the drill, as shown in **Figure 9**.

The speed of the drill is controlled by varying the width of the pulses.

The student decides to build a speed controller using the system diagram in Figure 10.

Figure 10

| astable | - | trigger<br>circuit | - | monostable | <b>-</b> | driver |

|---------|---|--------------------|---|------------|----------|--------|

|---------|---|--------------------|---|------------|----------|--------|

| 5 (a) | He decides to use a 555 timer IC in the astable circuit. He uses a 1 $k\Omega$ resistor for $R_{\rm A}$ |

|-------|---------------------------------------------------------------------------------------------------------|

|       | and a $100~\text{k}\Omega$ resistor for $R_{\text{B}}$ .                                                |

|       |                                                                                                         |

Calculate the value of the timing capacitor he will need to use for an output frequency of 10 Hz

|       | [3 marks]                                                                                                                                                         |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                                                                                                                                                   |

|       |                                                                                                                                                                   |

|       |                                                                                                                                                                   |

|       |                                                                                                                                                                   |

| 5 (b) | The student also decides to use a 555 timer IC for the monostable.  Describe the signal that should be provided by the trigger circuit to trigger the monostable. |

|       | [2 marks]                                                                                                                                                         |

|       |                                                                                                                                                                   |

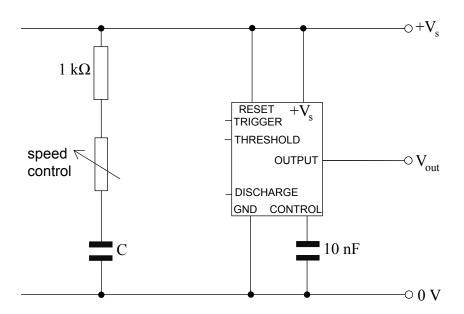

**5 (c) Figure 11** shows a partially completed circuit diagram for a 555 timer monostable.

Figure 11

5 (c) (i) Complete the circuit diagram by adding the missing connections.

Label with the word **input** where the signal from the trigger circuit should be connected.

[3 marks]

| 5 (c) (ii) | State why the | $k\Omega$ resistor i | is needed in | the circuit. |

|------------|---------------|----------------------|--------------|--------------|

|------------|---------------|----------------------|--------------|--------------|

[1 mark]

.....

**5** (c) (iii) The timing capacitor C has a value of 150 nF.

Calculate the maximum value of the variable resistor needed for full control of the speed of the motor.

[2 marks]

11

According to semiconductor theory, the forward voltage across a silicon diode increases linearly with temperature, so long as the current through the diode remains constant.

When a current of 1~mA passes through a particular diode, a student measures a forward voltage of 0.619~V at 0~°C and 0.718~V at 100~°C.

Show, using a calculation, that the change in voltage per  $^{\circ}C$  is approximately  $10^{-3} \text{ V/}^{\circ}C$ .

| [1 | mark] |

|----|-------|

|----|-------|

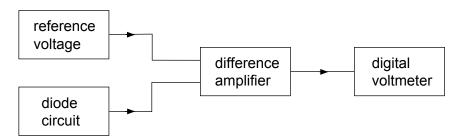

**6 (b)** The student decides to use this diode for a room thermometer project and devises the system diagram in **Figure 12**.

Figure 12

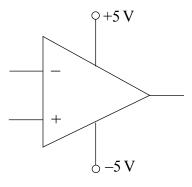

Complete the circuit diagram in **Figure 13** for a difference amplifier by adding **four** resistors.

[4 marks]

Figure 13

| 6 (c) | The output display for the room thermometer is a $0$ to $5$ V digital voltmeter that represents temperatures from $0$ °C to $50$ °C. Show, using a calculation, that the difference amplifier needs to have a voltage gain of 100. |  |

|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|       | [3 marks]                                                                                                                                                                                                                          |  |

|       |                                                                                                                                                                                                                                    |  |

|       |                                                                                                                                                                                                                                    |  |

| 6 (d) | The student uses $15~\mathrm{k}\Omega$ input resistors in his difference amplifier. Calculate the value that both the other resistors must have to produce a voltage gain of 100.                                                  |  |

|       | [3 marks]                                                                                                                                                                                                                          |  |

|       |                                                                                                                                                                                                                                    |  |

|       |                                                                                                                                                                                                                                    |  |

11

# END OF QUESTIONS