| Centre Number       |  |  | Candidate Number |  |  |

|---------------------|--|--|------------------|--|--|

| Surname             |  |  |                  |  |  |

| Other Names         |  |  |                  |  |  |

| Candidate Signature |  |  |                  |  |  |

General Certificate of Education Advanced Subsidiary Examination June 2012

# **Electronics**

ELEC2

## **Unit 2 Further Electronics**

Friday 18 May 2012 1.30 pm to 2.30 pm

### For this paper you must have:

- a pencil and ruler

- a calculator

- a Data sheet (enclosed).

#### Time allowed

• 1 hour

#### Instructions

- Use black ink or black ball-point pen.

- Fill in the boxes at the top of this page.

- Answer all questions.

- You must answer the questions in the spaces provided. Do not write outside the box around each page or on blank pages.

- Do all rough work in this book. Cross through any work you do not want to be marked.

#### Information

- The marks for questions are shown in brackets.

- The maximum mark for this paper is 67.

## Answer all questions in the spaces provided.

- **1** A student decides to use D-type flip-flops to make a controller for a motor.

- **1 (a)** Complete the truth table below for a D-type flip-flop.

| S | R | D | СК  | Q | Q |

|---|---|---|-----|---|---|

| 0 | 1 | 1 | 0   |   |   |

| 1 | 0 | 0 | 0   |   |   |

| 0 | 0 | 1 | 1 0 |   |   |

| 0 | 0 | 0 | 1 0 |   |   |

(4 marks)

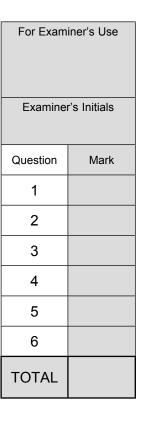

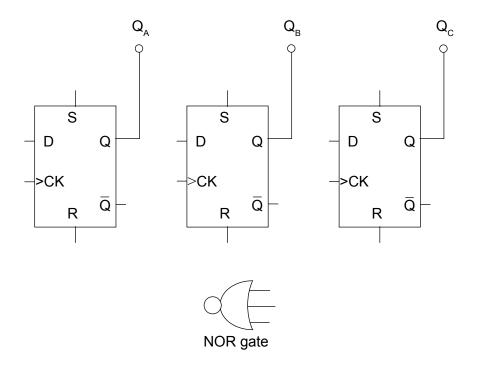

**1 (b)** Complete the circuit diagram below for a 4-bit shift register.

Label the data input and clock input to the shift register.

(4 marks)

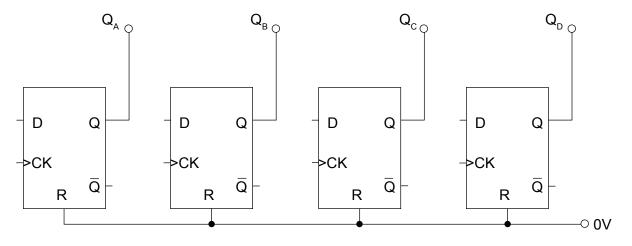

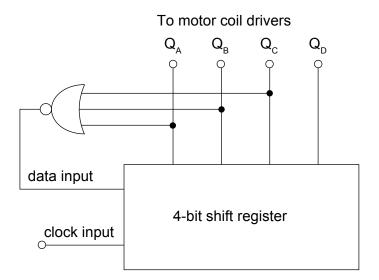

1 (c) The motor has four separate coils which are energised in turn to rotate the motor spindle. To achieve this a 3-input NOR gate is connected as shown in the diagram below.

Complete the timing diagram for the next 6 clock pulses.

(3 marks)

11

Turn over ▶

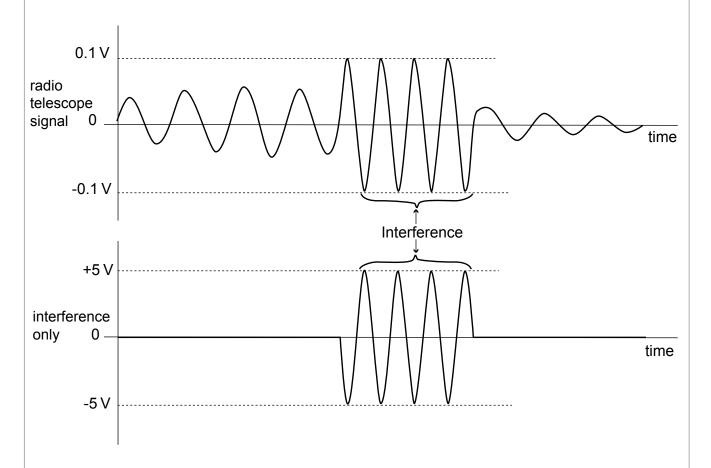

A radio telescope suffers interference from local industrial equipment. To reduce the interference it is decided to combine the radio telescope output signal with the signal from a receiver that receives only the interference.

The two signals are shown below.

Before the signals are combined, the interference signals must have the same amplitude. This is achieved by amplifying the radio telescope signal.

| 2 (a) (ı) | Calculate the voltage gain needed from this amplifier. |

|-----------|--------------------------------------------------------|

|           |                                                        |

|           |                                                        |

(3 marks)

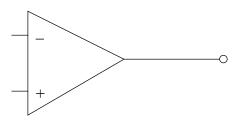

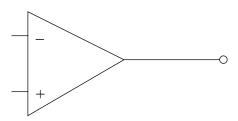

**2 (a) (ii)** It is decided to use a non-inverting amplifier where the voltage gain can be adjusted from 11 to approximately 100.

Complete the circuit diagram for the non-inverting amplifier and include suitable values for the resistors.

(3 marks)

- **2 (b)** The amplified radio telescope signal and the interference signal are added together with a summing amplifier.

- **2 (b) (i)** Complete the circuit diagram below for a summing amplifier and include suitable values for the resistors.

| $\circ$ | $\sim 0.1$ |

|---------|------------|

|         | U V        |

(3 marks)

2 (b) (ii) Explain how adding the two signals reduces the interference signal in the output.

.....

(2 marks)

11

Turn over ▶

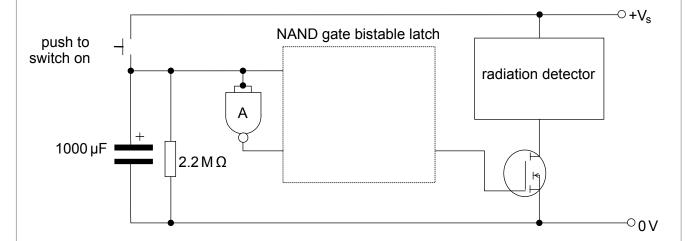

To prevent a portable radiation detector from being left switched on when not in use, the manufacturer incorporates the circuit below to switch the detector on for a fixed period of time.

| 3 (a) | Draw the logic diagram for the NAND gate bistable latch in the space above. | (4 marks) |

|-------|-----------------------------------------------------------------------------|-----------|

| 3 (b) | What is the function of NAND gate A?                                        |           |

| <b>O</b> (13)         | What is the fallotion of that B gate 7t.                                                                                                                                                         |           |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|

| 3 (c)                 | Calculate the time constant of the RC circuit.                                                                                                                                                   | (1 mark)  |

| <b>C</b> ( <b>G</b> ) |                                                                                                                                                                                                  |           |

|                       |                                                                                                                                                                                                  |           |

|                       |                                                                                                                                                                                                  | (3 marks) |

| 3 (d)                 | The NAND gates treat an input voltage of $>\frac{1}{2}V_s$ as logic 1 and $<\frac{1}{2}V_s$ as logic 0 Calculate the time that the detector remains switched on after the button is prereleased. |           |

|                       |                                                                                                                                                                                                  |           |

|                       |                                                                                                                                                                                                  |           |

|                       |                                                                                                                                                                                                  | (3 marks) |

|                       |                                                                                                                                                                                                  |           |

3 (e) Why is this circuit more effective than simply connecting the gate of the MOSFET to the timing circuit and missing out the bistable latch?

(1 mark)

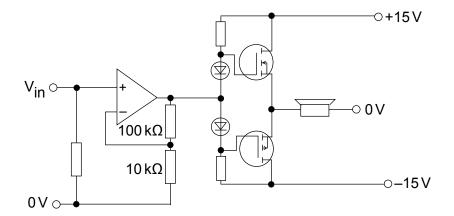

**4** A student constructs a push-pull amplifier for an electric guitar using the circuit below.

| 4 (a) | Each MOSFET is arranged as a source follower. State and justify approximate values |

|-------|------------------------------------------------------------------------------------|

|       | for the following properties of a MOSFET source follower.                          |

| 4 (a) (i)   | Voltage gain                                                            |

|-------------|-------------------------------------------------------------------------|

|             |                                                                         |

| 4 (a) (ii)  | Power gain                                                              |

|             |                                                                         |

| 4 (a) (iii) | Input resistance                                                        |

|             |                                                                         |

|             | (4 marks)                                                               |

| 4 (b)       | What is the function of the resistor and diode networks in the circuit? |

|             |                                                                         |

Question 4 continues on the next page

Turn over ▶

(1 mark)

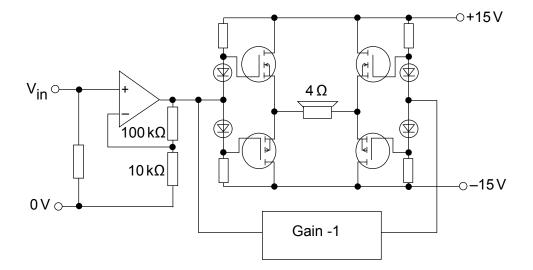

**4 (c)** The student finds on a web site that he can increase the output power by using the circuit shown in the diagram below.

| 4 (c) (i)  | Calculate the voltage gain of the op-amp subsystem.                            |      |

|------------|--------------------------------------------------------------------------------|------|

|            |                                                                                |      |

|            | (2 mai                                                                         |      |

| 4 (c) (ii) | Estimate the voltage gain of the complete circuit.                             | K3)  |

| + (o) (ii) | Louinate the voltage gain of the complete choult.                              |      |

|            | (1 ma                                                                          | эrk) |

| 4 (d)      | Estimate, using a calculation, the maximum rms output power of this amplifier. |      |

|            |                                                                                |      |

|            |                                                                                |      |

|            | (3 mai                                                                         |      |

11

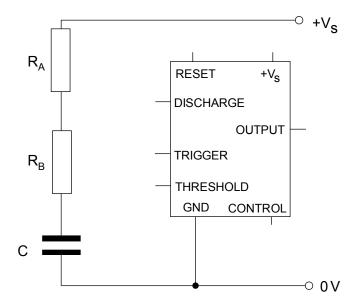

**5 (a)** Complete the circuit diagram below for a 555 astable.

(5 marks)

| 5 (b) | Calculate the frequency of the astable if $R_A = R_B = 10 \text{ k}\Omega$ and $C = 100 \text{ pF}$ . |

|-------|-------------------------------------------------------------------------------------------------------|

|-------|-------------------------------------------------------------------------------------------------------|

| <br>          |

|---------------|

| <br>          |

| <br>(3 marks) |

Question 5 continues on the next page

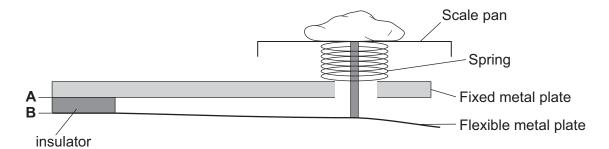

**5 (c)** A kitchen weighing machine has a weight sensor, which acts as a variable capacitor, as shown below.

When a load is placed on the scale pan, the flexible metal plate bends, so decreasing the capacitance of the variable capacitor formed by the two metal plates.

When there is no load on the scale pan the variable capacitor has a value of 25 pF. It is connected in parallel with the timing capacitor, C, in the 555 astable circuit.

| 5 (c) | State the effect on the output frequency of the astable when a load is added to the scale pan. |  |  |  |  |  |

|-------|------------------------------------------------------------------------------------------------|--|--|--|--|--|

|       | Give a reason for your answer.                                                                 |  |  |  |  |  |

|       |                                                                                                |  |  |  |  |  |

|       |                                                                                                |  |  |  |  |  |

|       |                                                                                                |  |  |  |  |  |

11

(3 marks)

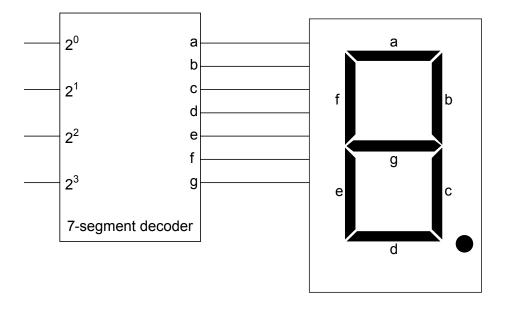

- A student wants to build an electronic dice for his coursework, which displays numbers on a 7-segment display. His supervisor suggests that he researches modulo-7 counters.

- **6 (a)** Complete the circuit diagram below for a modulo-7 counter which counts from 0 to 6 and then resets. Label the input from the clock.

(5 marks)

**6 (b)** The 7-segment display is interfaced to the counter with a 7-segment decoder.

Label on the diagram below where each of the inputs to the 7-segment decoder should be connected.

(4 marks)

Turn over ▶

| 6 (c) | When the student has built the circuit he is disappointed to find that the number 0 is displayed. His supervisor suggests modifying the circuit so that the counter resets to 1 instead of 0.  What changes should the student make to the circuit? |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                                                                                                                                                                                                                                     |

|       |                                                                                                                                                                                                                                                     |

|       | (2 marks)                                                                                                                                                                                                                                           |

11

## **END OF QUESTIONS**

Copyright  $\ensuremath{\texttt{@}}$  2012 AQA and its licensors. All rights reserved.