| Centre Number       |  |  | Candidate Number |  |  |

|---------------------|--|--|------------------|--|--|

| Surname             |  |  |                  |  |  |

| Other Names         |  |  |                  |  |  |

| Candidate Signature |  |  |                  |  |  |

General Certificate of Education Advanced Subsidiary Examination June 2011

# **Electronics**

ELEC2

## **Unit 2 Further Electronics**

Thursday 19 May 2011 9.00 am to 10.00 am

### For this paper you must have:

- a pencil and ruler

- a calculator

- a Data sheet.

#### Time allowed

• 1 hour

#### Instructions

- Use black ink or black ball-point pen.

- Fill in the boxes at the top of this page.

- Answer all questions.

- You must answer the questions in the spaces provided. Do not write outside the box around each page or on blank pages.

- Do all rough work in this book. Cross through any work you do not want to be marked.

#### Information

- The marks for questions are shown in brackets.

- The maximum mark for this paper is 67.

## Answer all questions in the spaces provided.

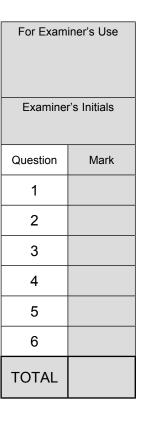

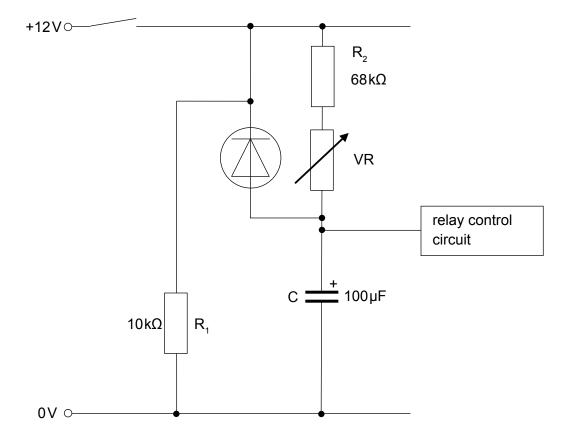

An audio system in a car has a relay which controls the output to the loudspeakers. This relay is controlled by an RC circuit, which gives a delay after the power is switched on, before the loudspeakers are connected. This prevents an unpleasant 'popping' noise which can happen when switching on.

| 1 (a) | Show that the time constant of the RC circuit in the diagram above is 6.8s. |           |

|-------|-----------------------------------------------------------------------------|-----------|

|       |                                                                             |           |

|       |                                                                             | (2 marks) |

**1 (b)** The capacitor is uncharged before the power is switched on.

**1 (b) (i)** The relay control circuit switches when the input is 6 V. Calculate the time delay before the loudspeakers are connected.

(3 marks)

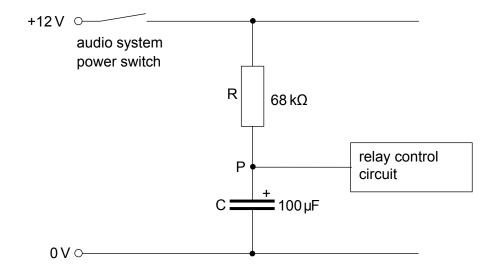

**1 (b) (ii)** On the axes below, sketch how the voltage at point P varies with time after the 12V supply is switched on. Add a scale to the time axis with time in seconds.

(2 marks)

Question 1 continues on the next page

1 (c) Three extra components are added to the circuit: a variable resistor (VR), a diode and a  $10\,\mathrm{k}\Omega$  resistor, as shown.

| (i) State the effect on the operation of the circuit of varying the resistance of VR.                                |         |

|----------------------------------------------------------------------------------------------------------------------|---------|

|                                                                                                                      |         |

|                                                                                                                      |         |

| (2 mark                                                                                                              | <br>(s) |

| c) (ii) When the power supply is switched off explain why the loudspeakers are quickly disconnected from the system. |         |

|                                                                                                                      |         |

|                                                                                                                      |         |

|                                                                                                                      |         |

| (2 mark                                                                                                              |         |

11

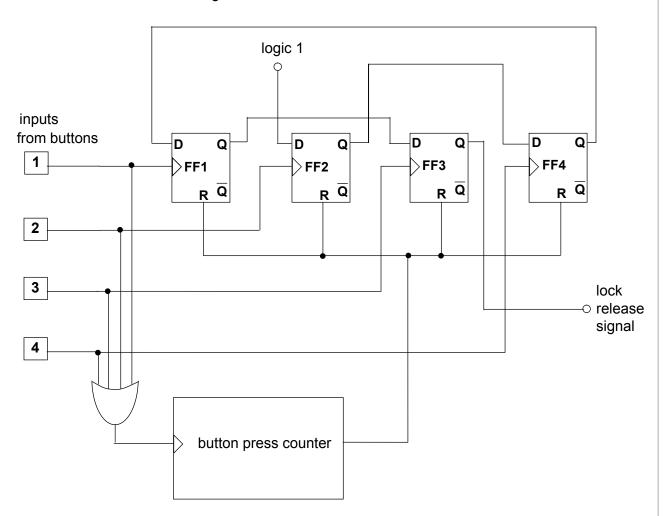

| 2     | An electronic combination lock is to be made using D-type flip-flops. |

|-------|-----------------------------------------------------------------------|

| 2 (a) | Describe the behaviour of a D-type flip-flop.                         |

|       |                                                                       |

|       |                                                                       |

|       |                                                                       |

|       | (4 marks)                                                             |

Part of the circuit diagram for the combination lock is shown below.

The design is based around four D-type flip-flops, and four buttons numbered 1, 2, 3 and 4. Each button generates a logic 1 when pressed and is connected to a D-type flip-flop. The circuit generates a high 'lock release' signal when the buttons are pressed in the correct order.

A counter counts the number of button presses, and resets the system if more than four presses have been made.

| 2 (b) | The system is reset, so that the Q outputs of all the flip-flops are at logic 0.                                       |            |  |  |

|-------|------------------------------------------------------------------------------------------------------------------------|------------|--|--|

|       | At this moment, explain why FF2 is the only flip-flop whose Q output will chawhen its corresponding button is pressed. |            |  |  |

|       |                                                                                                                        |            |  |  |

|       |                                                                                                                        |            |  |  |

|       | (3 /                                                                                                                   | <br>marks) |  |  |

| 2 (c) | Explain why the next button that should be pressed is 4.                                                               |            |  |  |

|       |                                                                                                                        |            |  |  |

|       | (2)                                                                                                                    | <br>marks) |  |  |

| 2 (d) | What is the complete four-digit lock release code?                                                                     |            |  |  |

|       |                                                                                                                        |            |  |  |

|       | (2)                                                                                                                    | <br>marks) |  |  |

|       |                                                                                                                        |            |  |  |

11

Turn over for the next question

- 3 The Health and Safety Officer in a factory requires a device to be fitted so that if the noise level exceeds 95dB a warning sign is switched on for 5 seconds or until the noise level decreases.

- The sound is detected by a microphone and is amplified by an inverting op-amp amplifier circuit, with a voltage gain of 82.

Draw a circuit diagram for the inverting op-amp amplifier circuit, and give suitable values for the resistors.

(4 marks)

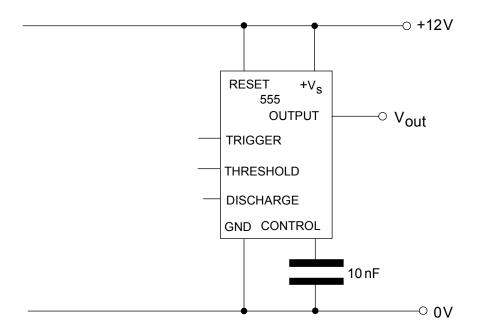

The electronics technician responsible for making the sign decides to use a 555 monostable to turn on the sign for the required period of time. Complete the circuit diagram below for a 555 monostable.

(4 marks)

| 3 (c) | On the diagram in part (b), label the input to the monostable.  (1 mark)                                                                                           |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 3 (d) | The technician decides to use a $150\mathrm{k}\Omega$ timing resistor. Calculate the value of the timing capacitor required to produce a time period of 5 seconds. |  |

|       |                                                                                                                                                                    |  |

|       |                                                                                                                                                                    |  |

|       | (2 marks)                                                                                                                                                          |  |

11

Turn over for the next question

- Stereo music recordings are made by having two separate microphones, one to the left and one to the right of the musicians. For these signals to be transmitted by radio they have to be processed so that a listener with a mono radio receives all of the information, while a listener with a stereo receiver can receive both the left and right channel signals separately.

- **4 (a)** For the mono radio listener, the left and right signals are added together and transmitted normally.

Draw the circuit diagram for an op-amp circuit that can add together two audio signals.

(3 marks)

**4 (b)** The magnitude of the voltage gain of the summing circuit is 1. On your diagram for part (a) mark suitable resistor values.

(2 marks)

**4 (c)** So that the two separate channels can be obtained for the stereo listener, the left and right signals are subtracted from each other, and this information is also transmitted but in a way that cannot be heard by the mono listener.

Draw the circuit diagram for an op-amp circuit that can subtract one signal from the other.

(3 marks)

| 4 (d) | The magnitude of the voltage gain of the subtraction circuit is 1. Mark on your diagram in part (c) suitable resistor values.  (2 marks) |

|-------|------------------------------------------------------------------------------------------------------------------------------------------|

| 4 (e) | The stereo radio receives two signals, L+R and L-R. Explain how the left and right signals can be extracted from these combined signals. |

|       |                                                                                                                                          |

|       |                                                                                                                                          |

|       |                                                                                                                                          |

|       | (2 marks)                                                                                                                                |

Turn over for the next question

A student wants to build a guitar practice amplifier and finds the circuit below on the internet.

| 5 (a) (i)  | State the input resistance of the amplifier.                              |              |

|------------|---------------------------------------------------------------------------|--------------|

|            |                                                                           | (1 mark)     |

| 5 (a) (ii) | Calculate the voltage gain of the op-amp subsystem.                       |              |

|            |                                                                           |              |

|            |                                                                           |              |

|            |                                                                           | (2 marks)    |

| 5 (b) (i)  | What is the name given to the circuit arrangement of the MOSFET subsystem | ?            |

|            |                                                                           | (1 mark)     |

| 5 (b) (ii) | Explain why the voltage gain of the entire circuit is approximately 4.9.  | , ,          |

|            |                                                                           |              |

|            |                                                                           |              |

|            |                                                                           | <br>(1 mark) |

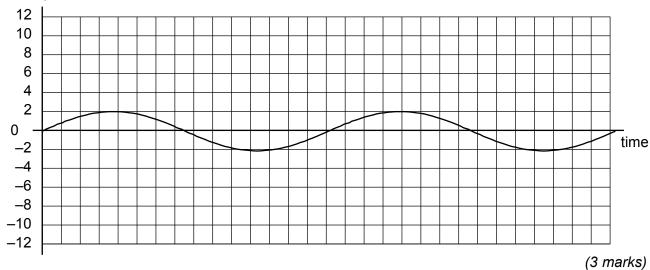

- 5 (c) The graphs below show the input signal to the amplifier.

- On the graph below draw the output signal from the op-amp. 5 (c) (i)

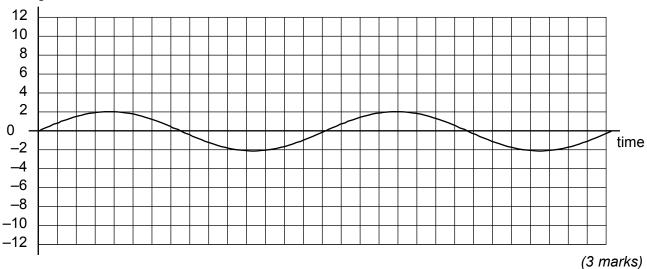

**5 (c) (ii)** On the graph below draw the signal across the speaker.

11

Turn over for the next question

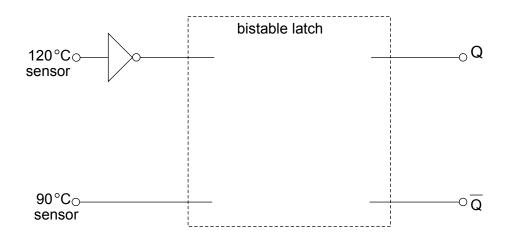

In order to ensure that a chemical product achieves the correct crystal structure, the manufacturer needs to repeat a cycle of warming the chemical to 120°C and then letting it cool to 90°C.

The chemical container has two temperature sensors; one gives logic 1 at or above 120 °C and logic 0 below and the other gives logic 1 at or above 90 °C and logic 0 below.

The temperature sensors are connected to the circuit below.

**6 (a)** Complete the circuit diagram for a NAND gate bistable latch.

(2 marks)

- **6 (b)** State the logic level of Q at the following stages as the chemical is being initially heated from cold

- 6 (b) (i) the chemical is cold .....

- **6** (b) (ii) the chemical reaches a temperature of 90 °C

- **6 (b) (iii)** the chemical reaches a temperature of 120 °C

- **6 (b) (iv)** the chemical temperature falls below 90 °C.

(4 marks)

**6 (c)** The heating and cooling cycle needs to be repeated six times and then the chemical is allowed to cool.

Complete the circuit diagram below for a modulo-6 counter.

(5 marks)

11

**END OF QUESTIONS**