## **General Certificate of Education**

## **Electronics** 5431/6431

**ELE2** Further Electronics

# **Mark Scheme**

2008 examination – June series

Mark schemes are prepared by the Principal Examiner and considered, together with the relevant questions, by a panel of subject teachers. This mark scheme includes any amendments made at the standardisation meeting attended by all examiners and is the scheme which was used by them in this examination. The standardisation meeting ensures that the mark scheme covers the candidates' responses to questions and that every examiner understands and applies it in the same correct way. As preparation for the standardisation meeting each examiner analyses a number of candidates' scripts: alternative answers not already covered by the mark scheme are discussed at the meeting and legislated for. If, after this meeting, examiners encounter unusual answers which have not been discussed at the meeting they are required to refer these to the Principal Examiner.

It must be stressed that a mark scheme is a working document, in many cases further developed and expanded on the basis of candidates' reactions to a particular paper. Assumptions about future mark schemes on the basis of one year's document should be avoided; whilst the guiding principles of assessment remain constant, details will change, depending on the content of a particular examination paper.

Further copies of this Mark Scheme are available to download from the AQA Website: www.aqa.org.uk

Copyright © 2008 AQA and its licensors. All rights reserved.

#### COPYRIGHT

AQA retains the copyright on all its publications. However, registered centres for AQA are permitted to copy material from this booklet for their own internal use, with the following important exception: AQA cannot give permission to centres to photocopy any material that is acknowledged to a third party even for internal use within the centre.

Set and published by the Assessment and Qualifications Alliance.

- **1** (a) E ✓

- (b) E.g. There are six occasions when the green light of traffic lights 1 is on and so each of these occasions must be **ORed** together. ✓ For each individual occasion, the logic state of the four counter outputs must be **ANDed** together to give logic 1. This means some of the counter outputs must be inverted. ✓

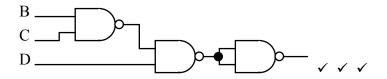

- (c) Karnaugh map or Boolean algebra to give  $G = D \cdot \overline{B \cdot C}$ One mark for each simplification.  $\checkmark \checkmark \checkmark$

(d)

Total - 9

- 2 (a) (i)  $V = I \times R = 10^7 \times 2 \times 10^{-10} \checkmark$ = 2 x 10<sup>-3</sup>V  $\checkmark$

- (ii)  $G_v = V_{out} / V_{in} = 200 \times 10^{-3} / 2 \times 10^{-3} \checkmark$ = 100  $\checkmark$

- (b) Very high impedance (resistance) input  $\checkmark$  This will not shunt the  $10M\Omega$  resistor of the ionisation chamber so lowering the output voltage  $\checkmark$

- (c) (i) Inverting amp connection to junction of 10M $\Omega$  resistor and R  $\checkmark$

- (ii) (Gv = 1 + Rf / R)=>  $100 = 1 + 10^7 / R \checkmark$ =>  $R = 10^7 / 99 = 101k\Omega \checkmark$

Total - 9

- **3** (a) (i) On the line joining the MOSFET to the transmitter

- (ii) (Source) follower (common drain amplifier) ✓

- (b) (i) Voltage divider **OR** 12V in the ratio of 1 : 2 ✓ Calculation ✓ => Voltage at non-inverting input is 8V

- (ii) Negative feedback attempts to reduce the difference between the two inputs to zero.

- => In the absence of an input signal both inputs will be at 8V so the output must be at 8V  $\checkmark$

- (iii) Two volts appear across the gate to source of the MOSFET so there will be 6V across the rf amplifier ✓

- (c) (i)  $G_v = -R_f / R_1 = -470 / 10 = (-)47 \checkmark$

(ii) If input is 40mV, then op-amp output is 1.88V ✓ Assume G<sub>v</sub> of source follower is 1 the voltage change across rf amplifier is also 1.88V ✓

Total - 9

- 4 (a) Inverting amplifier with a voltage gain of 200 / 10 = 20  $\checkmark$  So with a 500mV input the output will be 10V  $\checkmark$

- (b)  $P_{rms} = V_p^2 / 2 \times R = 10^2 / 2 \times 8 = 100 / 16 \checkmark = 6.25W \checkmark$

- (c) (i) Cross over distortion, when neither of the output transistors conducts at small (input) output voltages ✓

- (ii) Diode **biasing** networks to **turn on** the output transistors ✓ Push-pull stage included in the (negative) feedback loop ✓

- (d) Large surface area ✓

Dark, matt colour ✓

Good conductor of heat ✓ (max 2)

Total - 9

- **5** (a) (i) Allows low frequencies to pass, ✓ but blocks high frequencies ✓

- (ii) The frequency at which the output voltage (gain) is 70% of the maximum output voltage (gain) ✓

- (b)  $X_c = 1 / 2 \pi f C \checkmark$   $X_c = 1 / 2 \times 3.142 \times 20 \times 10^{-7} \checkmark$  $X_c = 79.6k\Omega \checkmark$

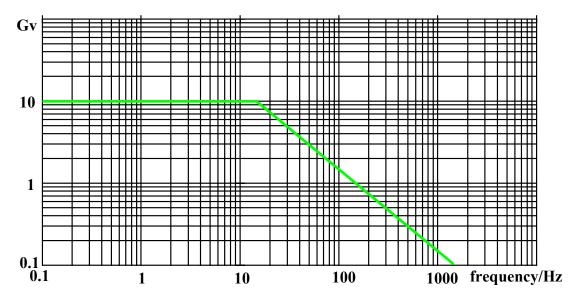

(c)

horizontal line to about 10-20Hz ✓ at a gain of 10 ✓ diagonal line - decreasing (at about 10 per decade) ✓

Total - 9

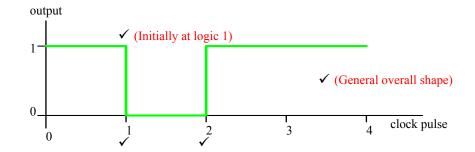

- 6 (a) For each flip-flop Q becomes D ✓

On the rising edge of the clock pulse ✓

Since D is connected to the previous Q, data is moved along the shift register (on each clock pulse) ✓

- (b) (i) Making S logic 0 will not set Q to 0

=> the shift register must be reset before the parallel

data is loaded ✓

- (ii) Logic 1 ✓

(c)

Total - 9

- 7 (a) (i)  $240 / 60 = 4\{Hz\} \checkmark$

- (ii)  $(f=1/2RC \Rightarrow) R = 1/2 \times 10^{-6} \times 4 \checkmark$ = 125k $\Omega \checkmark$

- (b) 30bpm = 0.5bps  $\checkmark$ => R = 1 / 2 x 10<sup>-6</sup> x 0.5 = 1M $\Omega$   $\checkmark$ (allow 825k $\Omega$  if calculated accurately)

- (c) (i)  $T = R \times C = 47 \times 10^{-9} \times 10^{5} \checkmark$ =  $47 \times 10^{-4} \text{s} = 4.7 \text{ms} \checkmark$

- (ii) This starts to charge capacitor C through resistor R and so makes the input of gate Y high. ✓

The output of gate Y goes low, which is fed back to gate X so keeping its output high. ✓

C charges through R until the input voltage to gate Y is below half of the supply voltage. ✓

The output of gate Y goes high, making output of gate X low, circuit resets. ✓

When input of gate X goes low the output of gate X goes high  $\checkmark$  (X = left gate, Y = middle gate) (max 4)

- (d) (i) D to Q for each flip-flop  $\checkmark$  CK of second flip-flop to  $\overline{Q}$  of the first flip-flop  $\checkmark$  Output of monostable to CK of first flip-flop  $\checkmark$

- (ii) LED lights if both Q<sub>A</sub> and Q<sub>B</sub> are logic 0 ✓

## (e) ✓ ✓ ✓ ✓

| No of Beats | $R_A$                                | $R_{B}$                            |

|-------------|--------------------------------------|------------------------------------|

| 2           | 0                                    | 1                                  |

| 3           | $Q_{\Lambda} \bullet Q_{\mathbb{P}}$ | 0.0                                |

| 3           | $\mathbf{Q}_{A}^{a}\mathbf{Q}_{B}$   | $\mathbf{Q}_{A}^{a}\mathbf{Q}_{B}$ |

(Max 3)

Total - 18

Paper Total - 72