A S S E S S M E N T and Q U A L I F I C A T I O N S A L L I A N C E

# Mark scheme June 2002

# GCE

## Electronics

### Unit ELE4

Copyright © 2002 AQA and its licensors. All rights reserved.

The Assessment and Qualifications Alliance (AQA) is a company limited by guarantee registered in England and Wales 3644723 and a registered charity number 1073334 Registered address: Addleshaw Booth & Co., Sovereign House, PO Box 8, Sovereign Street, Leeds LS1 1HQ Kathleen Tattersall: *Director General*

#### **Electronic Control Systems**

| 1 | (a) | (i) | data bus ، |

|---|-----|-----|------------|

|---|-----|-----|------------|

- (ii)  $\operatorname{clock} \checkmark$

- (iii) RAM  $\checkmark$

- (iv) input port  $\checkmark$

- (v) address bus  $\checkmark$

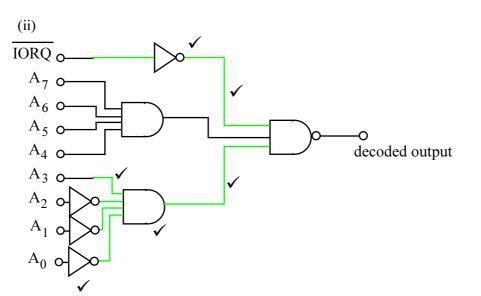

- (b) (i) Memory mapping is when an I/O port appears as part of the memory, whereas I/O mapping is when the I/O ports are addressed separately to the memory ✓

(5)

(6 max 4)

3

4

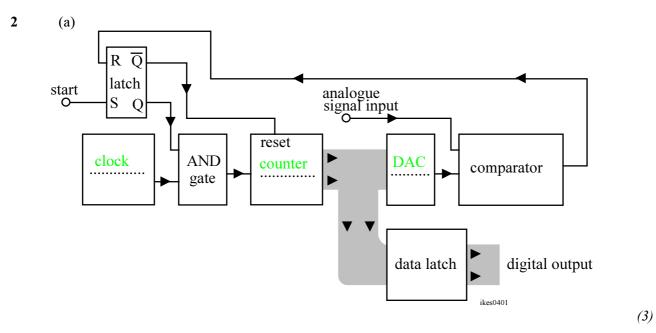

(b) (i) op-amp ✓ because it has a very large voltage gain and gives minimal indecision as to which input has the larger voltage.  $\checkmark$ (2)(ii) from DAC analogue signal input Vout 0 V o----(2) (c) Flash ADCs give very fast conversion times. This is not needed in this application.  $\checkmark$ (1) (8) summing amplifier  $\checkmark$ (i) (a) (1) (ii) calculation  $\checkmark$ -0.3125V ✓ (2)(iii) 10, 20, 40, 80, 160, 320, 640, 1280kΩ ✓ ✓ (2)(b) Data latch needed to capture the data from the data bus when the data is written to the output port (i) (ii) to hold the data steady while the DAC makes the conversion.  $\checkmark$   $\checkmark$ (ii) (2) (7) (a) significantly cheaper  $\checkmark$ allows for greater flexibility  $\checkmark$ mechanical timers have moving parts which wear  $\checkmark$ (max 2)(b) a PIC contains a microprocessor, ROM, RAM and I/O ports ✓ ie it is a computer fabricated on a single piece of silicon  $\checkmark$ Do not need external devices to operate  $\checkmark$ (max 2)

(c)

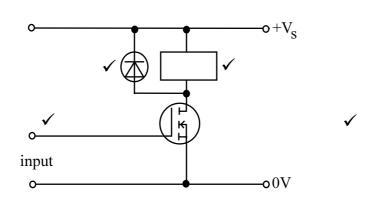

Input to gate and no series resistor, MOSFET symbol correct, relay in drain lead, diode across relay.

(4)

| AC    | A   |                            | GCE: Electronics – ELE4 Ju                                                                                                                                                                                                                                                                 | ine 2002 |

|-------|-----|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 5 (a) |     | (i)                        | The angular position of the armature is directly controlled by the control system so its angular speed is accurately controlled. $\checkmark$                                                                                                                                              |          |

|       |     |                            | system so its angular speed is accurately controlled.                                                                                                                                                                                                                                      | (1)      |

|       |     | (ii)                       | it is very expensive to have high power stepper motors ✓<br>do not normally rotate as fast as 3000rpm ✓                                                                                                                                                                                    | (-)      |

|       |     |                            |                                                                                                                                                                                                                                                                                            | (max 1)  |

|       | (b) | deterr<br>a disk<br>rotate | al shaft encoder enables the angular position of an axle to be accurately<br>nined. Usually a photo emitter and photo detector are positioned either side of<br>which has accurately positioned slots. The disk is attached to the axle and<br>as with the axle.<br>$\tan \sqrt{\sqrt{2}}$ |          |

|       |     |                            |                                                                                                                                                                                                                                                                                            | (3)      |

|       | (c) | (i)                        | Closed loop system $\checkmark$<br>Because the position of the motor axle is fed back to the microprocessor<br>controller via the shaft encoder $\checkmark$                                                                                                                               |          |

|       |     |                            | controller via the shart encoder .                                                                                                                                                                                                                                                         | (2)      |

|       |     | (ii)                       | Negative feedback $\checkmark$<br>If the motor is rotating too fast the system will slow it down                                                                                                                                                                                           |          |

|       |     |                            | and vice versa $\checkmark \checkmark$                                                                                                                                                                                                                                                     | (3)      |

|       |     |                            |                                                                                                                                                                                                                                                                                            | (10)     |

|       | (a) |                            | $V_{in}$ $2M\Omega$ $+5V$ $V_{out}$ $V_{out}$ $V_{out}$ $V_{out}$ $V_{out}$ $V_{out}$ $V_{out}$ $V_{out}$ $V_{out}$                                                                                                                                                                        |          |

|       | (b) | (i)                        | 201 🗸                                                                                                                                                                                                                                                                                      | (4)      |

|       |     | (ii)                       | Limited by the power supply voltage which is $\pm 5V$ . $\checkmark$                                                                                                                                                                                                                       | (1)      |

|       | (c) | (i)                        | Multiple crossings of zero volt line as waveform change state so leading to errors $\checkmark$                                                                                                                                                                                            | (1)      |

|       |     | (ii)                       | Calculation $\checkmark$ , $\pm 2.5 V \checkmark$                                                                                                                                                                                                                                          | (1)      |

|       |     | (iii)                      | The output of the schmitt trigger only changes state when the switching levels have been exceeded $\checkmark$ multiple transitions as the output changes state are therefore eliminated. $\checkmark$                                                                                     | (2)      |

|       |     |                            |                                                                                                                                                                                                                                                                                            | (2)      |

(2)

(11)

| AQA |

|-----|

|-----|

| 7 | (a) | (i)                 | Assume output of first NAND gate low, output of astable high $\checkmark$<br>Capacitor discharges and charges in opposite direction $\checkmark$<br>Until voltage at input to first NAND gate $<+V_s/2$ $\checkmark$<br>Output of astable switches state $\checkmark$<br>Capacitor charges in opposite direction $\checkmark$<br>Process repeats $\checkmark$                                           |            |

|---|-----|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

|   |     |                     |                                                                                                                                                                                                                                                                                                                                                                                                         | max 5)     |

|   |     | (ii)                | effective capacitance is $25nF \checkmark$                                                                                                                                                                                                                                                                                                                                                              | (1)        |

|   |     | (iii)               | $f = 1/2RC \Longrightarrow$ substitution to get 2kHz $\checkmark$                                                                                                                                                                                                                                                                                                                                       |            |

|   | (b) | to act i<br>Interru | g - computer repeatedly reads state of port looking for the appropriate change upon $\checkmark$<br>upon $\checkmark$ approximate the computer continues with other activities until the required change and then it stops what it was doing and processes the event $\checkmark$                                                                                                                       | (1)<br>(2) |

|   | (c) | (i)                 | A% = INP(&H379) read into A% the data on input port &H379 $\checkmark$<br>A% = A% AND X% AND the value in A% with the astable number and<br>restore in A% $\checkmark$<br>LOOP UNTIL A% = X% continue the process until A% is equal to the<br>astable number X% $\checkmark$<br>A% = A% XOR A% XOR A% with itself and restore in A%. Has the effect<br>of setting A% to 0, (Reset A% to 0) $\checkmark$ |            |

|   |     | (ii)                | Road C because it is connected to D <sub>2</sub> . (If X% is 4 then when ANDed with A% it will mask all other inputs by setting them to 0) $\checkmark$                                                                                                                                                                                                                                                 | (4)        |

|   | (d) | (i)                 | A neural network has a large number of simple processing units, which all process a small proportion of the data, but in parallel whereas a conventional computer has a single processing unit through which all data passes (Information stored in neurons) $\checkmark \checkmark$                                                                                                                    | (1)        |

|   |     | (ii)                | A neural network is able to learn and so would be able to control all of the traffic lights to maximise the throughput of traffic so reducing travelling time and pollution. Disadvantage is that if it gets it wrong or fails then the whole city becomes grid-locked.<br>(Cannot back up in case of failure) $\checkmark \checkmark$                                                                  | (2)        |

(18)