| Surname     | Centre<br>Number | Candidate<br>Number |

|-------------|------------------|---------------------|

| Other Names |                  | 2                   |

# GCE AS/A level

1141/01

# **ELECTRONICS – ET1**

A.M. MONDAY, 21 January 2013

| For Examiner's use only |                 |                 |  |  |

|-------------------------|-----------------|-----------------|--|--|

| Question                | Maximum<br>Mark | Mark<br>Awarded |  |  |

| 1.                      | 5               |                 |  |  |

| 2.                      | 2               |                 |  |  |

| 3.                      | 7               |                 |  |  |

| 4.                      | 8               |                 |  |  |

| 5.                      | 11              |                 |  |  |

| 6.                      | 7               |                 |  |  |

| 7.                      | 8               |                 |  |  |

| 8.                      | 12              |                 |  |  |

| Total                   | 60              |                 |  |  |

#### ADDITIONAL MATERIALS

In addition to this examination paper, you will need a calculator.

#### INSTRUCTIONS TO CANDIDATES

Use black ink or black ball-point pen.

Write your name, centre number and candidate number in the spaces at the top of this page.

Answer all questions.

Write your answers in the spaces provided in this booklet.

### INFORMATION FOR CANDIDATES

The total number of marks available for this paper is 60.

The number of marks is given in brackets at the end of each question or part-question.

You are reminded of the necessity for good English and orderly presentation in your answers.

You are reminded to show all working. Credit is given for correct working even when the final answer given is incorrect.

## INFORMATION FOR THE USE OF CANDIDATES IN ET1

## **Preferred Values for resistors**

The figures shown below and their decade multiples and sub-multiples are the E24 series of preferred values.

10, 11, 12, 13, 15, 16, 18, 20, 22, 24, 27, 30, 33, 36, 39, 43, 47, 51, 56, 62, 68, 75, 82, 91.

## **Standard Multipliers**

| Prefix | Multiplier        |

|--------|-------------------|

| Т      | $\times 10^{12}$  |

| G      | × 10 <sup>9</sup> |

| M      | $\times 10^6$     |

| k      | $\times 10^3$     |

| Prefix | Multiplier          |

|--------|---------------------|

| m      | × 10 <sup>-3</sup>  |

| μ      | × 10 <sup>-6</sup>  |

| n      | $\times 10^{-9}$    |

| р      | × 10 <sup>-12</sup> |

Operational amplifier

$$G = -\frac{R_F}{R_{IN}}$$

$$G = 1 + \frac{R_F}{R_1}$$

Slew Rate =

$$\frac{\Delta V_{OUT}}{\Delta t}$$

**Boolean identities**

$$A + \overline{A} \cdot B = A + B$$

$$A.B + A = A.(B+1) = A$$

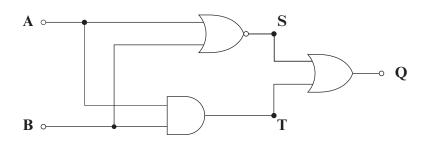

[3]

(a) Complete the truth table for the signal at points S, T and Q.

| В | A | S | T | Q |

|---|---|---|---|---|

| 0 | 0 |   |   |   |

| 0 | 1 |   |   |   |

| 1 | 0 |   |   |   |

| 1 | 1 |   |   |   |

(b) (i) Name the single gate that can replace the combination of gates above. [1]

(ii) Draw the logic symbol for this gate. [1]

© WJEC CBAC Ltd. (1141-01) Turn over.

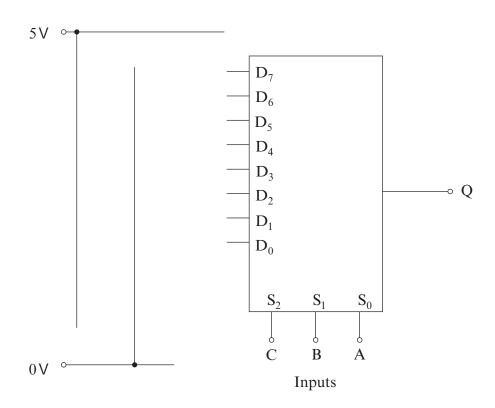

2. Multiplexers can be used as programmable logic systems. Complete the diagram to show how the 8:1 multiplexer can be used to create the output Q of the truth table. The input S<sub>2</sub> is the **most significant** select input. [2]

| С | В | A | Q |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

**3.** (a) Simplify the following Boolean expression.

$\overline{A}.0 = \dots$

(b) A Karnaugh map is shown below.

| $\setminus$ BA | <b>\</b> |    |    |    |

|----------------|----------|----|----|----|

| DC             | 00       | 01 | 11 | 10 |

| 00             | 1        | 0  | 1  | 1  |

| 01             | 0        | 0  | 1  | 0  |

| 11             | 0        | 0  | 1  | 0  |

| 10             | 1        | 0  | 1  | 1  |

Give the simplest Boolean expression for the output Q of this logic system. Show on the Karnaugh map, any groups that you have created in producing this expression.

| Q = 0 | <br> | <br> |  |

|-------|------|------|--|

|       |      |      |  |

|       |      |      |  |

$$Q = \overline{A.B + \overline{A}}$$

Apply DeMorgans theorem to the following expression and simplify the result.

[3]

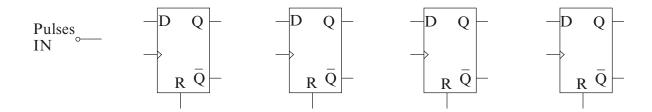

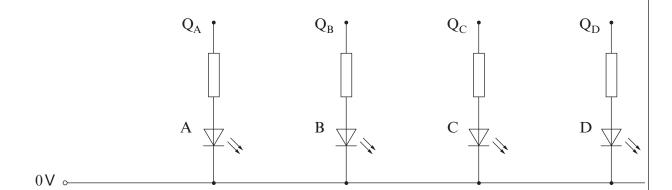

- 4. A system counts pulses and displays the count in binary on 4 LEDs (A, B, C and D).

- (a) Complete the diagram for the 4-bit binary up counter. The least significant bit of the counter must be connected to the LED labelled A. [3]

- (b) On the circuit diagram add a logic gate and the connections necessary to make the counter reset on the 10<sup>th</sup> clock pulse. [3]

- (c) Initially all the LEDs are OFF.

- (i) How many pulses have been counted if LEDs B and C are on and LEDs A and D are off?

(ii) What will be the logic levels of the following outputs after 9 pulses?

$$Q_A = \dots \qquad Q_D = \dots \qquad [1]$$

[3]

1141 010007

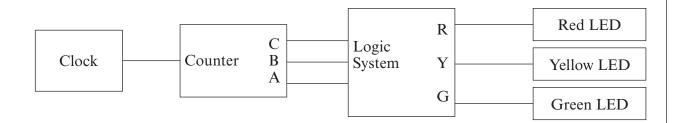

5. Two students design different light sequencers based on the following block diagram.

(a) The first student has a logic system specified by the following Boolean expressions:

$$R = \overline{B.A}$$

$$Y = \overline{B}$$

$$G = \overline{C}.B + C.\overline{B}.\overline{A}$$

Complete the truth table below to show the sequence of outputs produced.

| Clock<br>Pulse | С | В | A | R | Y | G |

|----------------|---|---|---|---|---|---|

| 0              | 0 | 0 | 0 |   |   |   |

| 1              | 0 | 0 | 1 |   |   |   |

| 2              | 0 | 1 | 0 |   |   |   |

| 3              | 0 | 1 | 1 |   |   |   |

| 4              | 1 | 0 | 0 |   |   |   |

| 5              | 1 | 0 | 1 |   |   |   |

| 6              | 1 | 1 | 0 |   |   |   |

| 7              | 1 | 1 | 1 |   |   |   |

Turn over.

© WJEC CBAC Ltd. (1141-01)

(b) The second student simulates traffic lights using the following truth table.

| Clock<br>Pulse | С | В | A | R | Y | G |

|----------------|---|---|---|---|---|---|

| 0              | 0 | 0 | 0 | 1 | 0 | 0 |

| 1              | 0 | 0 | 1 | 1 | 0 | 0 |

| 2              | 0 | 1 | 0 | 1 | 0 | 0 |

| 3              | 0 | 1 | 1 | 1 | 1 | 0 |

| 4              | 1 | 0 | 0 | 0 | 0 | 1 |

| 5              | 1 | 0 | 1 | 0 | 0 | 1 |

| 6              | 1 | 1 | 0 | 0 | 0 | 1 |

| 7              | 1 | 1 | 1 | 0 | 1 | 0 |

The clock frequency is 0.1 Hz.

| (i) | Use the table to determine for how long output R is at logic 1. | [1] |

|-----|-----------------------------------------------------------------|-----|

|     |                                                                 |     |

|     |                                                                 |     |

(ii) Use the table to write down the Boolean expressions for outputs R and Y in terms of inputs A, B and C. [1]

| R |  |

|---|--|

| v |  |

(iii) The student has partially simplified the G output to obtain

$$G = C.\overline{A} + C.\overline{B}.A$$

Using either a Karnaugh map or Boolean algebra simplify the expression for G. [3]

| <br>$\setminus$ BA |    |    |    |    |

|--------------------|----|----|----|----|

| $\mathbf{c}$       | 00 | 01 | 11 | 10 |

| 0                  |    |    |    |    |

| 1                  |    |    |    |    |

|   | (iv) | Design a suitable logic system using logic gates. Complete the following diagram with your design. [3] | ( |

|---|------|--------------------------------------------------------------------------------------------------------|---|

| A | 0    | —— R                                                                                                   |   |

|   |      |                                                                                                        |   |

| В | 0    | ——∘ Y                                                                                                  |   |

|   |      |                                                                                                        |   |

| C | o    | ——∘ G                                                                                                  |   |

Examiner only

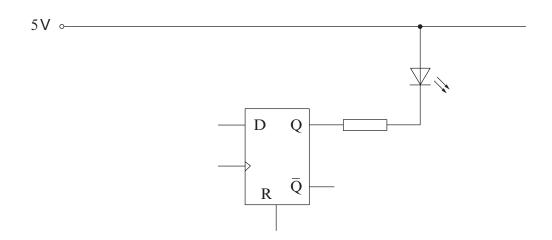

**6.** The diagram shows a *rising-edge triggered* D-type flip-flop. R is *active high*.

0V -

- (a) Add the necessary components to the diagram such that the D-type can be **reset** with the momentary press of a switch. [2]

- (b) Complete the following sentence. [1]

Examiner only

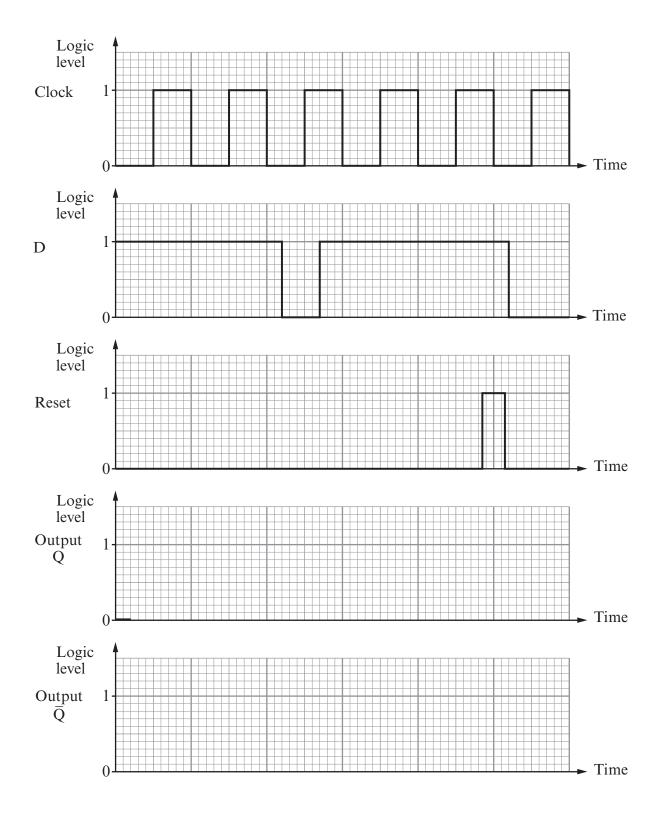

(c) The signals shown in the timing diagrams below are applied to the *rising-edge triggered* D-type. Complete the timing diagram for the outputs Q and Q. [4] **The RESET is** *active high*.

[3]

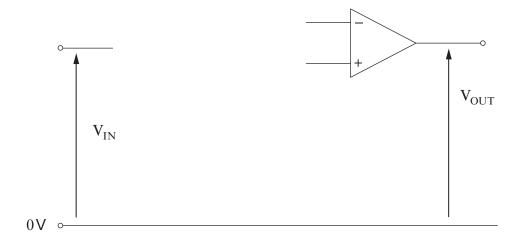

7. (a) Complete the circuit diagram for an inverting voltage amplifier.

| (c) How could the input impedance of the amplifier be changed without changing the gain? | (b) | Label the circuit diagram with suitable resistor values to give an input impedanc $10\mathrm{k}\Omega$ and a voltage gain of $-120$ . | e o [2] |

|------------------------------------------------------------------------------------------|-----|---------------------------------------------------------------------------------------------------------------------------------------|---------|

|                                                                                          | (c) |                                                                                                                                       | the     |

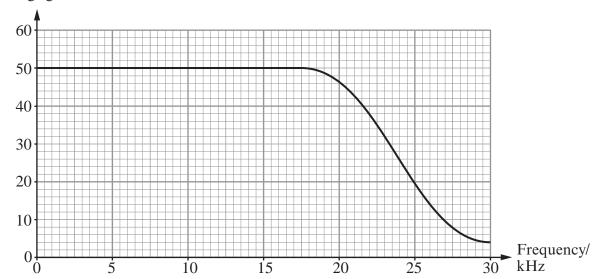

(d) Another amplifier has the frequency response shown below. Use the graph to estimate the bandwidth of this amplifier. Show **on the graph** how you obtained your result. [2]

Voltage gain

Bandwidth = kHz.

**8.** An extract from the data sheet of an op-amp is shown in the following table.

| Parameter              | Value                  |

|------------------------|------------------------|

| Input Impedance        | 10 MΩ                  |

| Output Impedance       | 100 Ω                  |

| Open Loop Gain         | 10 <sup>6</sup>        |

| Gain Bandwidth Product | 1.2 MHz                |

| Slew rate              | 5.0 V μs <sup>-1</sup> |

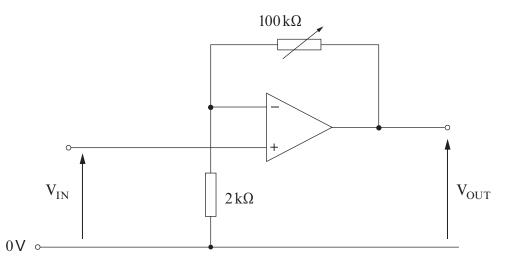

The circuit diagram shows the op-amp set up as a voltage amplifier. The *variable resistor* allows the user to change the gain. The value of this resistor can be altered from 0 to  $100 \, \text{k}\Omega$ .

The op-amp is powered from a  $\pm$  15 V supply and saturation occurs at  $\pm$  14 V.

| (a) | Wha  | at is the input impedance of this amplifier?                                                                         | [1]     |

|-----|------|----------------------------------------------------------------------------------------------------------------------|---------|

| (b) | Calc | rulate the maximum and minimum voltage gain of the amplifier.                                                        | [2]     |

|     | Max  | imum gain =                                                                                                          |         |

|     | Min  | imum gain =                                                                                                          |         |

| (c) | (i)  | The variable resistor is adjusted to give a voltage gain of 30. Calculate bandwidth of the amplifier with this gain. | the [2] |

|     |      |                                                                                                                      |         |

Examiner only

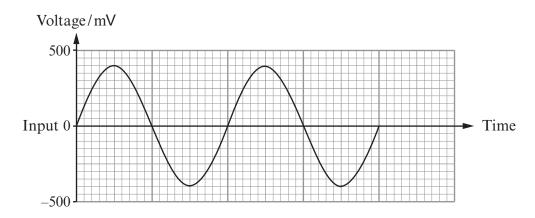

(ii) With the voltage gain set to 30 the following signal is applied to the input. Draw the output signal on the axes provided. Label important voltage values on the axes. [3]

| (iii)                                   | What would be the maximum input voltage that would avoid clipping distort | ion?<br>[1] |

|-----------------------------------------|---------------------------------------------------------------------------|-------------|

|                                         |                                                                           |             |

| *************************************** |                                                                           |             |

|                                         |                                                                           |             |

# TURN OVER FOR THE REST OF THE QUESTION

| (d) | (i)   | Calculate the time taken for the output to change from 0 V to 14 V in response to a large step-change in input voltage. Give an appropriate unit. [2] | 0 |

|-----|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---|

|     | (ii)  | Give one advantage of having a high slew rate. [1]                                                                                                    |   |

|     | ••••• |                                                                                                                                                       |   |

## **END OF PAPER**