| Surname     | Centre<br>Number | Candidate<br>Number |

|-------------|------------------|---------------------|

| Other Names |                  | 0                   |

# **GCE A level**

1145/01

# ELECTRONICS ET5

P.M. THURSDAY, 31 May 2012

$1\frac{1}{2}$  hours

| For Examiner's use only |                 |                 |  |  |  |  |

|-------------------------|-----------------|-----------------|--|--|--|--|

| Question                | Maximum<br>Mark | Mark<br>Awarded |  |  |  |  |

| 1.                      | 6               |                 |  |  |  |  |

| 2.                      | 9               |                 |  |  |  |  |

| 3.                      | 8               |                 |  |  |  |  |

| 4.                      | 6               |                 |  |  |  |  |

| 5.                      | 8               |                 |  |  |  |  |

| 6.                      | 4               |                 |  |  |  |  |

| 7.                      | 8               |                 |  |  |  |  |

| 8.                      | 8               |                 |  |  |  |  |

| 9.                      | 7               |                 |  |  |  |  |

| 10.                     | 6               |                 |  |  |  |  |

| Total                   | 70              |                 |  |  |  |  |

## ADDITIONAL MATERIALS

In addition to this examination paper, you will need a calculator.

#### INSTRUCTIONS TO CANDIDATES

Use black ink or black ball-point pen.

Write your name, centre number and candidate number in the spaces at the top of this page.

Answer all questions.

Write your answers in the spaces provided in this booklet.

#### INFORMATION FOR CANDIDATES

The total number of marks available for this paper is 70.

The number of marks is given in brackets at the end of each question or part-question.

You are reminded of the necessity for good English and orderly presentation in your answers.

You are reminded to show all working. Credit is given for correct working even when the final answer given is incorrect.

#### INFORMATION FOR THE USE OF CANDIDATES

#### **Preferred Values for resistors**

The figures shown below and their decade multiples and sub-multiples are the E24 series of preferred values.

10, 11, 12, 13, 15, 16, 18, 20, 22, 24, 27, 30, 33, 36, 39, 43, 47, 51, 56, 62, 68, 75, 82, 91.

**Standard Multipliers**

| Prefix | Multiplier         |

|--------|--------------------|

| Т      | × 10 <sup>12</sup> |

| G      | × 10 <sup>9</sup>  |

| M      | × 10 <sup>6</sup>  |

| k      | × 10 <sup>3</sup>  |

| Prefix | Multiplier         |

|--------|--------------------|

| m      | $\times 10^{-3}$   |

| μ      | $\times 10^{-6}$   |

| n      | × 10 <sup>-9</sup> |

| p      | $\times 10^{-12}$  |

**Alternating Voltages**

$$V_o = V_{rms} \sqrt{2}$$

Silicon Diode

$$V_F \approx 0.7V$$

Operational amplifier

$$G = -\frac{R_F}{R_{IN}}$$

$$G = 1 + \frac{R_F}{R_1}$$

$$V_{OUT} = V_{DIFF} \left( \frac{R_F}{R_1} \right)$$

$$V_{OUT} = -R_F \left( \frac{V_1}{R_1} + \frac{V_2}{R_2} + \frac{V_3}{R_3} \right)$$

$$V_{L} \approx V_{Z} \left( 1 + \frac{R_{F}}{R_{1}} \right)$$

**Emitter follower**

$$V_{OUT} = V_{IN} - 0.7V$$

**Filters**

$$f_b = \frac{1}{2\pi RC}$$

$$X_{C} = \frac{1}{2\pi fC}$$

Thyristor phase control

$$\phi = \tan^{-1} \frac{R}{X_C}$$

$$\tan \phi = \frac{R}{V}$$

Signal conversion

$$tan \phi = \frac{R}{X_C}$$

$$resolution = \frac{i/p \text{ voltage range}}{2^n}$$

Power amplifier

$$P_{MAX} = \frac{V_S^2}{8R_L}$$

where

$$V_S$$

is the rail-to-rail voltage

#### **PIC Information**

The PIC programs include 'equate' statements that define the following labels:

| Label  | Description                         |

|--------|-------------------------------------|

| PORTA  | input / output port A               |

| PORTB  | input / output port B               |

| TRISA  | the control register for port A     |

| TRISB  | the control register for port B     |

| STATUS | the status register                 |

| INTCON | the interrupt control register      |

| W      | the working register (= h '0')      |

| F      | the file register (= h '1')         |

| RP0    | the register page selection bit 0   |

| Z      | the zero flag status bit            |

| GIE    | the global interrupt controller bit |

| INTE   | the external interrupt enable bit   |

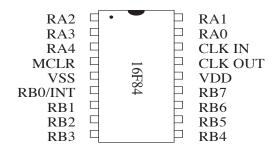

Pin out for 16F84 PIC IC:

#### List of commands:

| Mnemonic                                                                                 | Operands                                | Description                                                                   |  |  |  |

|------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------|--|--|--|

| bcf                                                                                      | f, b                                    | Clear bit b of file f                                                         |  |  |  |

| bsf                                                                                      | f, b                                    | Set bit b of file f                                                           |  |  |  |

| btfss                                                                                    | f, b                                    | Test bit b of file f, skip next instruction if bit is set                     |  |  |  |

| call k Call subroutine k                                                                 |                                         | Call subroutine k                                                             |  |  |  |

| clrf f                                                                                   |                                         | Clear file f                                                                  |  |  |  |

| goto k Branch to labe                                                                    |                                         | Branch to label k                                                             |  |  |  |

| <b>movf</b> f, d Move file f (to itself if $d = 1$ , or to working register if $d = 0$ ) |                                         | Move file f (to itself if $d = 1$ , or to working register if $d = 0$ )       |  |  |  |

| movlw k Move literal k to working register                                               |                                         | Move literal k to working register                                            |  |  |  |

| movwf                                                                                    | movwf f Move working register to file f |                                                                               |  |  |  |

| retfie                                                                                   |                                         | Return from interrupt service routine and set global interrupt enable bit GIE |  |  |  |

#### Comparison of TASM and MPASM languages:

| Ver                    | sion     | TASM      | MPASM         |

|------------------------|----------|-----------|---------------|

|                        | Decimal  | 153       | d'153'        |

| Number system notation | Hex      | \$2B      | h'2B' or 0x2B |

| notation               | Binary   | %10010110 | b'10010110'   |

|                        |          | .equ      | equ           |

| Ongodo                 | Notation | .org      | org           |

| Opcode Notation        |          | .end      | end           |

|                        |          | label:    | label         |

### Structure of the INTCON register

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| GIE   | EEIE  | TOIE  | INTE  | RBIE  | TOIF  | INTF  | RBIF  |

### Structure of the STATUS register

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| IRP   | RP1   | RP0   | TO    | PD    | Z     | DC    | С     |

| 1. | (a)<br> |      | n stage in a synchronous counter is clocked at the same time. What advantage does give synchronous counters over ripple counters? [1] |

|----|---------|------|---------------------------------------------------------------------------------------------------------------------------------------|

|    | (b)     | Sync | chronous counters are prone to a problem caused when unused states are also stuckes.                                                  |

|    |         | (i)  | Explain what is meant by:                                                                                                             |

|    |         |      | unused states; [1]                                                                                                                    |

|    |         |      | stuck states. [1]                                                                                                                     |

|    |         | (ii) | When does the problem caused by stuck states occur? [1]                                                                               |

|    |         |      |                                                                                                                                       |

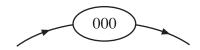

(c) The behaviour of a synchronous counter is defined by its state diagram.

Use the table below to draw the state diagram for this 3-bit synchronous counter.

[2]

|       | ( | Current Outpu | ıt |         | Next Output |       |

|-------|---|---------------|----|---------|-------------|-------|

| State | С | В             | A  | $D_{C}$ | $D_{B}$     | $D_A$ |

| 0     | 0 | 0             | 0  | 0       | 0           | 1     |

| 1     | 0 | 0             | 1  | 0       | 1           | 1     |

| 2     | 0 | 1             | 1  | 1       | 1           | 0     |

| 3     | 1 | 1             | 0  | 1       | 0           | 0     |

| 4     | 1 | 0             | 0  | 0       | 0           | 0     |

| 5     | 0 | 1             | 0  | 0       | 0           | 0     |

| 6     | 1 | 0             | 1  | 1       | 1           | 1     |

| 7     | 1 | 1             | 1  | 1       | 0           | 0     |

1145 010005

# **BLANK PAGE**

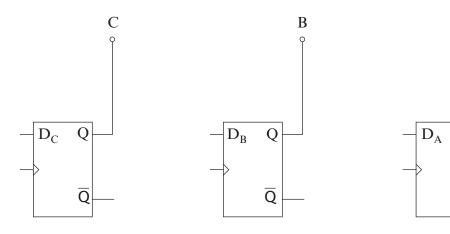

2. A sequence generator is controlled by the following Boolean expressions.

$$D_C = \overline{C.A}$$

$$D_B = C \oplus A$$

$$D_A = \overline{A} + C.\overline{B}$$

(a) Complete the circuit diagram for this sequence generator. (Credit will be given for using the minimum number of gates.)

[5]

A

$\overline{Q}$

1145 010007

Clock o\_\_\_\_

(b) Complete the table to show the sequence of outputs generated by these Boolean expressions: [4]

|       | ( | Current Outpu | ıt |         | Next Output |       |

|-------|---|---------------|----|---------|-------------|-------|

| State | С | В             | A  | $D_{C}$ | $D_B$       | $D_A$ |

| 0     | 0 | 0             | 0  |         |             |       |

| 1     |   |               |    |         |             |       |

| 2     |   |               |    |         |             |       |

| 3     |   |               |    |         |             |       |

| 4     |   |               |    |         |             |       |

| 5     |   |               |    |         |             |       |

| 6     |   |               |    |         |             |       |

| 7     |   |               |    |         |             |       |

|              | The following code is written to the data direction registers of a PIC microcontroller: |                                                       |                        |                                                               |     |

|--------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------|------------------------|---------------------------------------------------------------|-----|

|              | mo                                                                                      | vlw<br>vwf<br>vlw<br>vwf                              | b'(<br>T1<br>b'(<br>T1 | CATUS,RP0<br>00111'<br>RISA<br>00000000'<br>RISB<br>CATUS,RP0 |     |

|              | Describe the eff                                                                        | ect of this                                           | s code on PO           | RT A of the microcontroller.                                  | [1] |

| (b)          | How does the m                                                                          | nicroconti                                            | roller locate t        | he Interrupt Service Routine?                                 | [1] |

|              | The PIC micro                                                                           | aantralla                                             |                        |                                                               |     |

| (c)          | delay subroutin  A Reset switch                                                         | e called 't                                           | hreesec' is av         | A bit 0.                                                      |     |

| ( <i>c</i> ) | delay subroutin  A Reset switch                                                         | e called 't is connect rrupt Serv                     | hreesec' is av         | ailable.                                                      |     |

|              | A Reset switch: Here is the Inter                                                       | e called 't is connect rrupt Serv listing. inter loop | hreesec' is av         | ailable. A bit 0.                                             |     |

| (ii)  | Describe exactly what is observed at the output when lines 102 to 106 of the program are executed. | he<br>3] |

|-------|----------------------------------------------------------------------------------------------------|----------|

|       |                                                                                                    |          |

|       |                                                                                                    |          |

|       |                                                                                                    |          |

| (iii) | State the purpose and effect of the instructions in lines 107 and 108 in the program.              | is<br>2] |

|       |                                                                                                    |          |

|       |                                                                                                    |          |

|       |                                                                                                    |          |

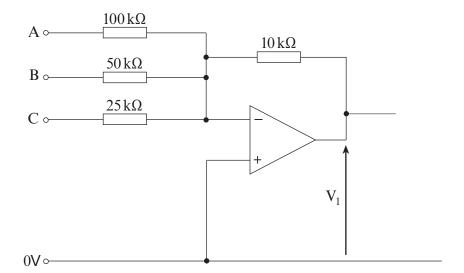

4. Here is the circuit diagram for a Digital-to-Analogue Converter (DAC). This system uses a 10V signal to represent logic 1 and a 0V signal to represent logic 0. The output of the op-amp saturates at +10V and -10V.

| (a)        | Calculate voltage $V_1$ when the digital number 001 is applied to the inputs. | [1] |

|------------|-------------------------------------------------------------------------------|-----|

|            |                                                                               |     |

|            | V -                                                                           |     |

| <i>(b)</i> | $V_1 =$                                                                       | [1] |

|            |                                                                               |     |

|            | V -                                                                           |     |

1145 010011

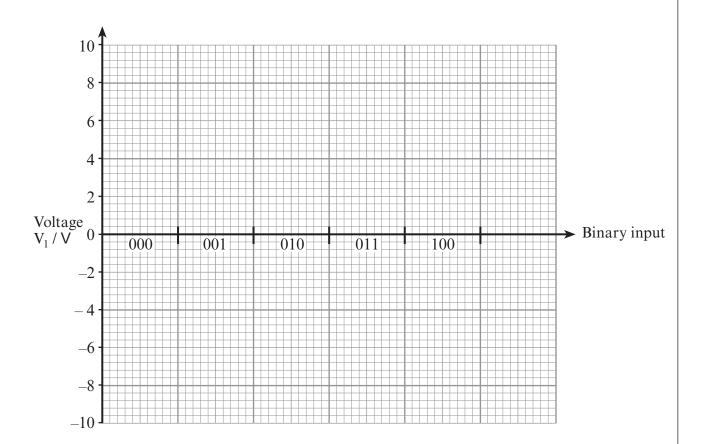

(c) Use the axes provided to draw a graph to show how voltage  $V_1$  changes as the binary input increases, in steps, from 000 to 100. [2]

(d) Modify the circuit diagram by adding a second amplifier, with a gain of -1, to invert the signal  $V_1$ .

Label any resistors used with suitable values. [2]

Turn over.

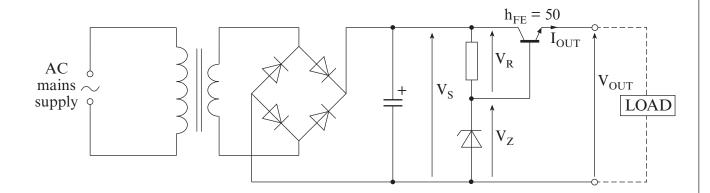

| 5.         | A high    | quality power | supply incorporates | line and le | oad regulation. |

|------------|-----------|---------------|---------------------|-------------|-----------------|

| <i>-</i> • | 7 1111511 | quality power | supply incorporates | inc and i   | oua regulation. |

| (a) | Explain what is meant by line regulation and load regulation. | [3] |

|-----|---------------------------------------------------------------|-----|

|     |                                                               |     |

|     |                                                               |     |

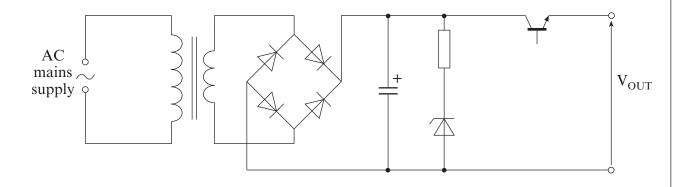

The diagram shows the circuit for a power supply. *(b)*

Calculate the output voltage  $\boldsymbol{V}_{OUT}$  when

•

$$V_S = 14V$$

•

$$V_S = 14V$$

•  $V_Z = 9.2V$  [1]

The performance can be improved by adding an op-amp voltage amplifier to the (c) circuit.

Show how this is done by modifying the following circuit diagram. Your modification should make it possible to vary the output voltage,  $V_{\rm OUT}$ .

No component values are needed.

[4]

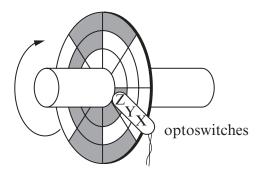

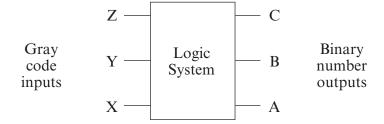

6. A machine tool control system uses an encoded disc to monitor how far a shaft has rotated. The disc is encoded using Gray code, and is read by three reflective optoswitches X, Y and Z. The arrangement is shown in the diagram.

| (a) | What is the advantage of using Gray code instead of pure binary code in tapplication? | his<br>[1] |

|-----|---------------------------------------------------------------------------------------|------------|

|     |                                                                                       |            |

|     |                                                                                       |            |

|     |                                                                                       |            |

(b) A logic system is needed to convert the Gray code output from the optoswitches into binary numbers.

The conversion table is shown below:

$A = \overline{Z}.(Y \oplus X) + Z.(\overline{Y \oplus X})$

| Gray code |   | Binary number |   |   |   |

|-----------|---|---------------|---|---|---|

| Z         | Y | X             | C | В | A |

| 0         | 0 | 0             | 0 | 0 | 0 |

| 0         | 0 | 1             | 0 | 0 | 1 |

| 0         | 1 | 1             | 0 | 1 | 0 |

| 0         | 1 | 0             | 0 | 1 | 1 |

| 1         | 1 | 0             | 1 | 0 | 0 |

| 1         | 1 | 1             | 1 | 0 | 1 |

| 1         | 0 | 1             | 1 | 1 | 0 |

| 1         | 0 | 0             | 1 | 1 | 1 |

| Obtain Boolean expressions for the binary number outputs, C and B, in terms of the Gray code inputs Z, Y and X. Output A has been done for you. Credit will be given for simplification. [3] |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                              |

|                                                                                                                                                                                              |

|                                                                                                                                                                                              |

|                                                                                                                                                                                              |

|                                                                                                                                                                                              |

| C =                                                                                                                                                                                          |

| B =                                                                                                                                                                                          |

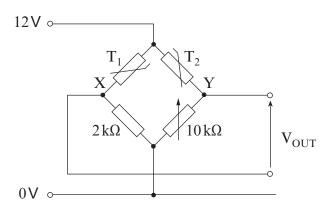

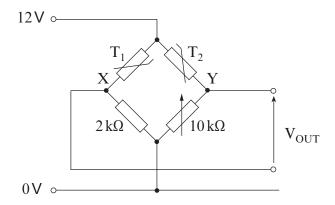

7. The following system is used to detect small temperature differences inside an enclosure. The circuit contains two thermistors,  $T_1$  and  $T_2$ , a 2 k $\Omega$  precision resistor and a variable resistor.

The circuit diagram is given below.

Initially, the resistances of the two thermistors are exactly  $1.5\,k\Omega$ .

- (a) What is the value of  $V_{OUT}$  when the variable resistor has a value of  $2.00 \, k\Omega$ ? [1]  $V_{OUT} = \dots$

- (b) Calculate the output voltage V<sub>OUT</sub> when:

- thermistor  $T_1$  has a resistance of  $1.43 \, k\Omega$

- thermistor  $T_2$  has a resistance of  $1.20 \, k\Omega$

- the variable resistor has a resistance of  $2.00 \,\mathrm{k}\Omega$

$V_{OUT} = \dots$

(c) Modify the circuit diagram by adding a difference amplifier connected to amplify  $V_{\rm OUT}$ . [2]

(d) Calculate suitable resistor values so that the amplifier has a voltage gain of 40.

Label all resistors used in the amplifier with their ideal values. [3]

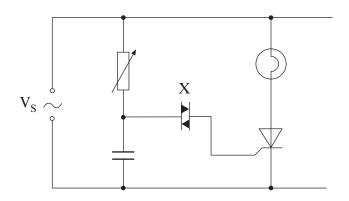

**8.** A thyristor is used to control the brightness of a lamp, using phase control. The circuit diagram is shown below:

(a) (i) Identify component X. [1]

.....

(ii) What is its function in this circuit? [1]

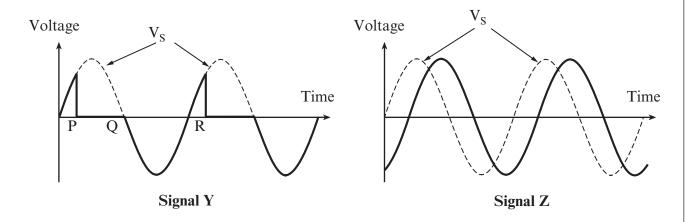

(b) The graphs show two signals obtained from parts of the circuit:

(i) Signal Y appears across which component? [1]

| (ii)  | State what is happening to the lamp:                       |     |

|-------|------------------------------------------------------------|-----|

|       | • between P and Q                                          | [1] |

|       | between Q and R                                            | [1] |

| (iii) | Signal Z appears across which component?                   | [1] |

| (iv)  | Name the effect shown in signal Z and state how it arises. | [2] |

|       |                                                            |     |

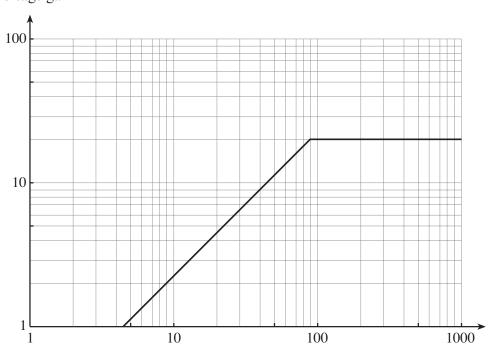

**9.** (a) The graph shows the frequency response of an active filter.

Voltage gain

Frequency / Hz

(i) What kind of filter is this?

[1]

(ii) What is the break frequency of this filter?

[1]

(iii) Complete the circuit diagram for the type of filter which produces the frequency response shown in the graph.

Component values are not needed.

[3]

Input o-

Output

0V o-

(iv) Why is this filter called an active filter?

[1]

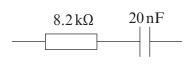

(b) The circuit for a **different** filter includes the RC combination shown below.

| Calculate the break frequency of this filter. |  |  |

|-----------------------------------------------|--|--|

|                                               |  |  |

|                                               |  |  |

|                                               |  |  |

|                                               |  |  |

|                                               |  |  |

|                                               |  |  |

Break frequency = ...... Hz

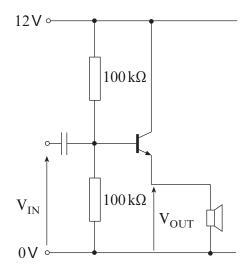

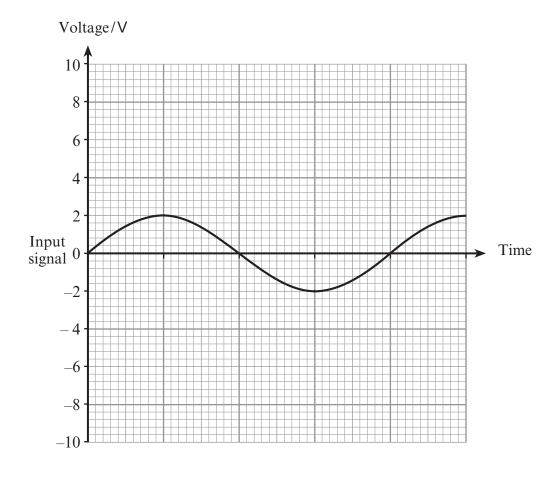

10. An audio system uses a power amplifier to drive the loudspeaker output stage.

Two possible choices for a power amplifier are the emitter follower and the push-pull amplifier.

(a) An emitter follower circuit is shown below.

The signal shown in the graph is applied to the input. Draw the output signal on the same axes.

[2]

| (b) | Complete the circuit diagram for a push-pull power | amplifier. [3                           |

|-----|----------------------------------------------------|-----------------------------------------|

|     | 12V -                                              |                                         |

|     | $V_{IN}$                                           | 0 V                                     |

|     | -12V ∘                                             |                                         |

| (c) | Give one advantage of a push-pull follower over an | emitter follower power amplifier.<br>[1 |

|     |                                                    |                                         |

# THERE ARE NO MORE QUESTIONS IN THE EXAMINATION

| ••   |

|------|

|      |

| ٠.   |

|      |

|      |

| <br> |

|      |

| ••   |

| ••   |

| <br> |

| ٠.   |

|      |

|      |

| <br> |

|      |

| ••   |

|      |

| <br> |

| <br> |

|      |

|      |

|      |

|      |

| ••   |

|      |

| ٠.   |

|      |

|      |

|      |

|      |

| ••   |

| ٠.   |